Hello! (quick disclaimer all of this is very new to me so if my questions sounds stupid I apologize in advance)

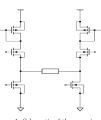

Consider this differential pair

I am using diode connected PMOS loads and external biasing done via the Ibias pin; I have one degeneration resistor and M12 and M13 are susposed to be a part of an enable circuit (it is to the left and connected to the differential pair but for the sake of readibilty I didnt post it). I am feeding Vin and Vip with an external single ended to differental circuit that looks like this;

And last but not least this is my test bench;

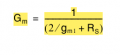

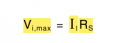

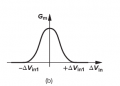

In my Ngspice terminal I have saved the small signal values of every transistor (gm,ids vgs,fug,cgg,vds..) and in my control block I am trying for one; to find my gm/id of the 2 NMOS transistors that have Vip and Vin attached to them so that with, that gm/id value i can get a realisitc value for my Ibias (i assummed that gm/id = 12 but my professor said this could be off). and after that I am trying to find my Gm in my input range from -1.2 to 1.2 and plot it out.

Now as for my understanding my goal firstly should be, that all of my transistors (expect my enable transistors since I want them to be switches) should be in saturation. And here comes the problem;

M6 and M2 are not in saturation, while M13 is;

I have tried everything I can think of to get M6 and M2 into saturation but I just cant; tried changing W and L, didnt help, tried increasing Ibias didnt help. Varied Rs from 1ohm to 1MOhm, didnt help, tried removing M13 didnt help. No matter what I do they wont be saturated so my gm plot is way off.

Any advice? What am I missing. Thanks in advance!

Consider this differential pair

I am using diode connected PMOS loads and external biasing done via the Ibias pin; I have one degeneration resistor and M12 and M13 are susposed to be a part of an enable circuit (it is to the left and connected to the differential pair but for the sake of readibilty I didnt post it). I am feeding Vin and Vip with an external single ended to differental circuit that looks like this;

And last but not least this is my test bench;

In my Ngspice terminal I have saved the small signal values of every transistor (gm,ids vgs,fug,cgg,vds..) and in my control block I am trying for one; to find my gm/id of the 2 NMOS transistors that have Vip and Vin attached to them so that with, that gm/id value i can get a realisitc value for my Ibias (i assummed that gm/id = 12 but my professor said this could be off). and after that I am trying to find my Gm in my input range from -1.2 to 1.2 and plot it out.

Now as for my understanding my goal firstly should be, that all of my transistors (expect my enable transistors since I want them to be switches) should be in saturation. And here comes the problem;

M6 and M2 are not in saturation, while M13 is;

I have tried everything I can think of to get M6 and M2 into saturation but I just cant; tried changing W and L, didnt help, tried increasing Ibias didnt help. Varied Rs from 1ohm to 1MOhm, didnt help, tried removing M13 didnt help. No matter what I do they wont be saturated so my gm plot is way off.

Any advice? What am I missing. Thanks in advance!

Attachments

-

78.6 KB Views: 1

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin