Hi everyone,

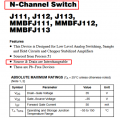

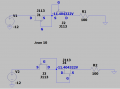

I’m simulating a bidirectional current limiter using two back-to-back N-channel JFETs. I came across this configuration in an op-amp protection circuit. The circuit seems to work fine—it limits the current regardless of the input voltage (see attached image). However, I noticed that one of the JFETs appears to behave like a diode, and I’m not fully sure why that happens. Could someone explain the reason behind this behavior?

Connetion: Used LT spice for simulation, J113 as njfet. Both sources are connected together and gates are tied together and shorted. (VGS is 0 for both).

Thanks!

I’m simulating a bidirectional current limiter using two back-to-back N-channel JFETs. I came across this configuration in an op-amp protection circuit. The circuit seems to work fine—it limits the current regardless of the input voltage (see attached image). However, I noticed that one of the JFETs appears to behave like a diode, and I’m not fully sure why that happens. Could someone explain the reason behind this behavior?

Connetion: Used LT spice for simulation, J113 as njfet. Both sources are connected together and gates are tied together and shorted. (VGS is 0 for both).

Thanks!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin