what is the frequency of oscillator circuit

- Thread starter Jagdish23

- Start date

Scroll to continue with content

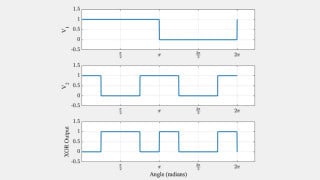

Hi Dana, thanks for the hint.Think in terms of phase angle, to get osc loop phase must be n x 360, inverter elements

contribute 180, so in this example they contribute 540, so you need how much phase out

of the RC's ?

Then back into what freq this occurs at.

Regards, Dana.

I too used the same hint and tried to solve the equation. but I get w(omega)=(1/RC*sqrt(6)) as the answer.

But for the same circuit, the answer given as is 1/(3.3RC). So the doubt generated in my mind to consider which answer as the correct one!!!

Regards,

Jagdish

MisterBill2

- Joined Jan 23, 2018

- 27,315

The symbol shows them as inverters, the frequency will also depend on the threshold voltages for switching, and that will usually depend on the temperature, and the logic family.

I think

eg. 60 degrees /section.

https://www.inictel-uni.edu.pe/site...blicaciones/12/rc_phase_shift_oscillators.pdf

Gate contribution toward f probably insignificant if f << 1/Tpd of Gate.

The circuit looks like its biased into the gate active region, so oscillation

a mix of small signal behavior and non linear (due to no amplitude control).

Regards, Dana.

eg. 60 degrees /section.

https://www.inictel-uni.edu.pe/site...blicaciones/12/rc_phase_shift_oscillators.pdf

Gate contribution toward f probably insignificant if f << 1/Tpd of Gate.

The circuit looks like its biased into the gate active region, so oscillation

a mix of small signal behavior and non linear (due to no amplitude control).

Regards, Dana.

Last edited:

MisterBill2

- Joined Jan 23, 2018

- 27,315

It is not the propagation delay that affects the frequency, it is the shifting of the voltages at which the gate changes state. And the change in Vhl may not be the same as the change in Vlh. And the switching point determines how far on the RC time constant curve the voltage must go for the thing to change, thus affecting the frequency in a non-linear manner. Of course, if you use perfect gates in a simple simulator this is not a problem. Real gates, such as cheap CD4001 NORs, with both inputs tied, are a different story.

Of course the prop delay affects frequency. In fact in semiconductor processing,

using 3 inverters in series feedback, on wafer test site, the freq is measured (and

largely dependent on Tpd, Vdd) to evaluate the Fmax of a process.

When you look at transfer curves of the inverter there is a substantial "linear"

region over which small signal behavior exists to create an osc.

Is there no relation to switching levels, no, Vdd very much impacts Vth, and G of

the inverter. But the osc can and will operate around the bias point which Vth is

very much involved. Main contribution to osc freq however is R and C, available

current and capacitance. Tpd directly impacted, Vth not so much.

The CMOS inverter structure is largely a linear G element. one with a RC lowpass

behavior. Switching speed characterized by available current to charge C, usually

expressed as prop delay.

http://bwrcs.eecs.berkeley.edu/Classes/icdesign/ee141_f01/Notes/chapter5.pdf

https://www.egr.msu.edu/classes/ece410/mason/files/Ch7.pdf

Regards, Dana.

using 3 inverters in series feedback, on wafer test site, the freq is measured (and

largely dependent on Tpd, Vdd) to evaluate the Fmax of a process.

When you look at transfer curves of the inverter there is a substantial "linear"

region over which small signal behavior exists to create an osc.

Is there no relation to switching levels, no, Vdd very much impacts Vth, and G of

the inverter. But the osc can and will operate around the bias point which Vth is

very much involved. Main contribution to osc freq however is R and C, available

current and capacitance. Tpd directly impacted, Vth not so much.

The CMOS inverter structure is largely a linear G element. one with a RC lowpass

behavior. Switching speed characterized by available current to charge C, usually

expressed as prop delay.

http://bwrcs.eecs.berkeley.edu/Classes/icdesign/ee141_f01/Notes/chapter5.pdf

https://www.egr.msu.edu/classes/ece410/mason/files/Ch7.pdf

Regards, Dana.

MisterBill2

- Joined Jan 23, 2018

- 27,315

The propagation delay is very small relative to the typical frequency of a common phase shift oscillator, and so while it will certainly have some effect it would not be very large at 1 Kilohertz. The variation in switch point voltage will have a larger effect, and with cheap CMOS that will matter. And in the really cheap consumer products, using a 4001 quad nor as a set of inverters is fairly common.Of course the prop delay affects frequency. In fact in semiconductor processing,

using 3 inverters in series feedback, on wafer test site, the freq is measured (and

largely dependent on Tpd, Vdd) to evaluate the Fmax of a process.

When you look at transfer curves of the inverter there is a substantial "linear"

region over which small signal behavior exists to create an osc.

Is there no relation to switching levels, no, Vdd very much impacts Vth, and G of

the inverter. But the osc can and will operate around the bias point which Vth is

very much involved. Main contribution to osc freq however is R and C, available

current and capacitance. Tpd directly impacted, Vth not so much.

The CMOS inverter structure is largely a linear G element. one with a RC lowpass

behavior. Switching speed characterized by available current to charge C, usually

expressed as prop delay.

http://bwrcs.eecs.berkeley.edu/Classes/icdesign/ee141_f01/Notes/chapter5.pdf

https://www.egr.msu.edu/classes/ece410/mason/files/Ch7.pdf

Regards, Dana.

I concur.The propagation delay is very small relative to the typical frequency of a common phase shift oscillator, and so while it will certainly have some effect it would not be very large at 1 Kilohertz.

I am in process of trying out a spice sim to see what happens.

My thought is Vth variation is like Tpd change, a small result. That

its RC changes that dominate. Hopefully the sim will give us an idea.

Regards, Dana.

The Electrician

- Joined Oct 9, 2007

- 2,986

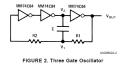

This formula only applies to the circuit of Fig. 2 of the referenced paper where the CR phase shifting pairs are separated from one another by unity gain buffers.I think View attachment 155434

eg. 60 degrees /section.

https://www.inictel-uni.edu.pe/site...blicaciones/12/rc_phase_shift_oscillators.pdf

Regards, Dana.

Without the buffers, as in Fig. 3, the formula no longer applies. As the author says just in front of Fig. 3: "If the RC cells were isolated from each other, the phase shift per cell would be 60º. However, not being it the case, we need to perform a detailed analysis considering loading effects. "

MisterBill2

- Joined Jan 23, 2018

- 27,315

In the initial posting there were indeed 3 separate cells,and probably the assumption that all three were identical, and with "perfect" inverters. What we find in the real world is that the inverters are not perfect and the components are seldom identical. The voltage to switch from low out to high out is not the same as the voltage to switch from high out to low out, and the current that the devices can sink is more that what they can source. And the voltages change with temperature, but not by the same amount. So running the circuit on a simulator will require specifying a whole lot of parameters, or picking a good part for the inverters. The circuit will run quite differently with a CD4049 then with a CD4009, OR A 74C04. and using a really cheap CD4001 with inputs tied will be different yet. Every part of the circuit will have an effect. As the difference between the two switch points increases the frequency will drop, likewise, as the current that the gate can source drops, so will the frequency.

Assuming F is << Tpd, probably formula still pretty good. Why, because the otherWithout the buffers, as in Fig. 3, the formula no longer applies.

180 has to come out of the 3 RC networks. To a first order. Clearly this design is

a mix of large signal, small signal, and non linear dynamics. It would be instructive

to look at actual spectrum to see how much impact the non linearities have.

Unity gain issue, yes true to a point. Again how impactfull are all these other factors.

We can surmise that until we actually make some measurements that all this is speculative.

But I know one constraint, the 3 RC have to provide 180 degrees if we find spectrum

close to sinusoidal.

I am away from primary lab so spectrum analysis is marginal, maybe FFT will be

enough.

Yes, but when we characterized parts for process standards we often found fairlyWhat we find in the real world is that the inverters are not perfect and the components are seldom identical.

good matching in Vth on single die, die to die on wafer, but central to edge

of wafer where dopant concentrations varied over that distance significantly Vth

quite sloppy.

Yes, the sim will need a lot of trial tweaking to see what contributes large errors

vs rats nuts sized issues. The Pchan mobility vs Nchan I concur issue. The structure

inherently unbalanced.

As far as the transfer characteristic H-L vs L-H, I only see one trajectory in published

CMOS graphic transfer characteristic. I must be missing something here ?

The whole idea of making an osc this way is filled with part and passive

tolerance, T, and V issues. But would be interesting just what and how

much do each of these factors contribute, and does the argument stand

each RC, if matched, do have to contribute 60 degrees.....

Fun stuff....

Regards, Dana.

Last edited:

MisterBill2

- Joined Jan 23, 2018

- 27,315

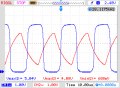

Jony, I am wondering about where in the circuit the waveforms shown are taken from. Or is it a simulation? I am especially puzzled by the lack of squareness of what should be a square wave. Please let us know which circuit, or variation, this is from. AND where the measurement points are located.I don't think so.

View attachment 155523

As you can see for R = 10kΩ and C = 1nF; Vdd = 5V the frequnct of oscilation is arond 28Khz.

So the formula for RC Phase-Shift Oscillator won't work in this case.

MisterBill2

- Joined Jan 23, 2018

- 27,315

The square wave does not look as square as I would anticipate for the points monitored. I had guessed that is what they were, but the rounded corners don't seem right. And you can see that while the top of the ramp wave is about in the center, the bottom is not, thus showing that there is a difference in the high and low switching points on the gate. With this being the 3-RC version it shows that using the RC time constant to find frequency is a bit more complicated, since each one is a third of the cycle time, and the rise is faster than the fall.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin