I want to build a counter and want to display it with 7 segment display. I will use a push button to give a clock pulse so this will be the enter button. What I want is, when the counter is 3 then it will lock my clock pulse or enter button. This means if I click the push button after count 3 it won't increase the counter or reset it. It will activate my buzzer and won't stop as long as I do not reset it.

So there will be a reset button to reset my counter. So when I click the reset button the counter will be reset to 0 and by enter button will work again.

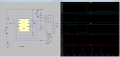

This is my schematic diagram. Here the reset button is working fine but when the counter is 3 it is resetting after clicking the enter button too. I've used much logic to prevent the pulse but could not find the solution.

So there will be a reset button to reset my counter. So when I click the reset button the counter will be reset to 0 and by enter button will work again.

This is my schematic diagram. Here the reset button is working fine but when the counter is 3 it is resetting after clicking the enter button too. I've used much logic to prevent the pulse but could not find the solution.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin