In the past when I have designed 4 layer PCBs I have used the following stackup....

I have just started desiging a new board and since learning tips from an EMI course (https://www.skool.com/pcb-design-mastery-9530) I have decided to try the following stackup....

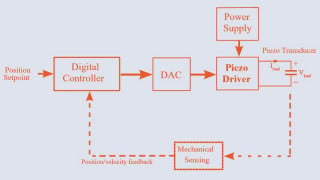

[Images from https://resources.altium.com/p/4-layer-pcb-stackup]

The stackup shown in option 1 has benefits for EMC and signal integrity, which is why I am attempting to try this stackup.

The stackup shown in option 3 makes it easy to connect to power (3.3V, 5V, VBUS etc) because there is power plane on layer 3.

But this is more difficult with option 1, because power is routed on the top and bottom layers with signals.

One EMI tip is to ensure there are no breaks in the ground plane, but there is no way I can route all the power tracks on top and bottom layers and a 6 layer board quadruples the cost.

Below is my design so far, but I have had to route power tracks on layer 3 (shown in orange) as well as layer 1 (shown in blue). I will fill layer 3 (orange) with GND once completed, but as I had to route some power tracks on layer 3 there will be breaks in the GND plane.

The questions I have are:

1. Is it ok to use tracks for power instead of planes ?

Presumably tracks will have more impedance than a large power plane ?

But for signal integrity and EMI, its critical that signals have a return reference plane (i.e. GND) underneath them.

2. Is it ok that there will be breaks in the GND plane on layer 3 (orange) ?

The board is very compact and uses devices such as an STM32, W25Q flash, bluetooth antenna (50R impedance), USB (90R impedance).

I have just started desiging a new board and since learning tips from an EMI course (https://www.skool.com/pcb-design-mastery-9530) I have decided to try the following stackup....

[Images from https://resources.altium.com/p/4-layer-pcb-stackup]

The stackup shown in option 1 has benefits for EMC and signal integrity, which is why I am attempting to try this stackup.

The stackup shown in option 3 makes it easy to connect to power (3.3V, 5V, VBUS etc) because there is power plane on layer 3.

But this is more difficult with option 1, because power is routed on the top and bottom layers with signals.

One EMI tip is to ensure there are no breaks in the ground plane, but there is no way I can route all the power tracks on top and bottom layers and a 6 layer board quadruples the cost.

Below is my design so far, but I have had to route power tracks on layer 3 (shown in orange) as well as layer 1 (shown in blue). I will fill layer 3 (orange) with GND once completed, but as I had to route some power tracks on layer 3 there will be breaks in the GND plane.

The questions I have are:

1. Is it ok to use tracks for power instead of planes ?

Presumably tracks will have more impedance than a large power plane ?

But for signal integrity and EMI, its critical that signals have a return reference plane (i.e. GND) underneath them.

2. Is it ok that there will be breaks in the GND plane on layer 3 (orange) ?

The board is very compact and uses devices such as an STM32, W25Q flash, bluetooth antenna (50R impedance), USB (90R impedance).

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin