I'm kind of going down a rabbit hole here. It started off with a simple enough question: "What is the simplest way to test for equality between two sets of bits?" The single-bit truth table of course looks like this:

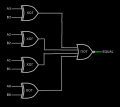

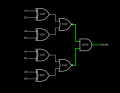

Which is obviously just the inverse of the XOR gate (ie. the XNOR gate). Chaining them together sequentially turned out to be a bit of a mess, so instead I decided on a much more sane approach: construct larger circuits from 4-bit sub-circuits:

Then I can just connect them together using a single AND gate for each stage. Like this:

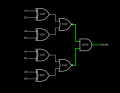

Looks pretty good to me. I can compare two N-bit numbers with just 2N logic gates. I wonder though, could it have been made with even less components?

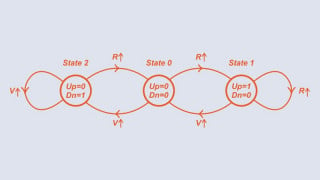

My second question is a little more complicated. Can I use a similar approach to build less-than and less-than-or-equal circuits? Consider a single-bit less-than circuit:

So basically AND the right-hand-side bit with the inverse (NOT) of the left-hand-bit. But when I tried chaining those together in a bunch of different ways I kept getting stuck. The two-bit version is almost the OR of two one-bit circuits, except for one particular case. Unfortunately, "fixing" that made things so convoluted that the idea of adding more of these together to make, say, 16-bit less-than circuits seemed completely ridiculous. Can anyone point me in the right direction?

Code:

= 0 1

0 1 0

1 0 1

Then I can just connect them together using a single AND gate for each stage. Like this:

Looks pretty good to me. I can compare two N-bit numbers with just 2N logic gates. I wonder though, could it have been made with even less components?

My second question is a little more complicated. Can I use a similar approach to build less-than and less-than-or-equal circuits? Consider a single-bit less-than circuit:

Code:

< 0 1

0 0 1

1 0 0

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin