Hi,

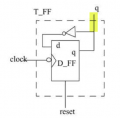

I was trying to understand the operation of a T Flip Flop. I have seen the diagram shown below in one of the books as well where input is applied at Q.

CE is an enable input and it is assumed that the flip flop is negative edge triggered.

Question:

If "1" is applied on Qn, the flip flop will produce 0 on Q(n+1). The same node Q is "1" and "0". Isn't it contradictory?

Source: https://www.cse.psu.edu/~kxc104/class/cmpen271/13f/hw/hw8/hw8.html

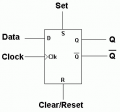

T flop flop truth table

I was trying to understand the operation of a T Flip Flop. I have seen the diagram shown below in one of the books as well where input is applied at Q.

CE is an enable input and it is assumed that the flip flop is negative edge triggered.

Question:

If "1" is applied on Qn, the flip flop will produce 0 on Q(n+1). The same node Q is "1" and "0". Isn't it contradictory?

Source: https://www.cse.psu.edu/~kxc104/class/cmpen271/13f/hw/hw8/hw8.html

T flop flop truth table

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin