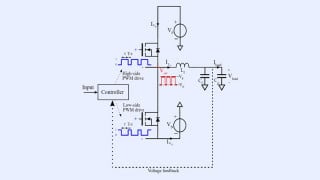

Hello , i have build a structure of two traces and via going threw a plane as shown below.

Its supposed to be purely inductive .

I know there is also place capacitance from the plane .I got Z11 imaginary part very negatice which means that its capacitative trace.

i didnt even put decoupling capacitors. where did i go wrong seeing the inductive behavior of the trace?

Thanks.

Its supposed to be purely inductive .

I know there is also place capacitance from the plane .I got Z11 imaginary part very negatice which means that its capacitative trace.

i didnt even put decoupling capacitors. where did i go wrong seeing the inductive behavior of the trace?

Thanks.

Attachments

-

59.4 KB Views: 0

-

57 KB Views: 0

-

56.5 KB Views: 0

-

70.1 KB Views: 0

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin