Hi:

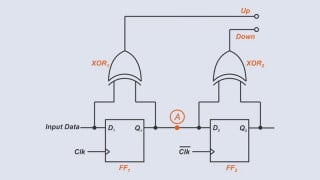

I am breadboarding a frequency counter. I have attached two circuits. Circuit #1 will hopefully perform

a gate control function and circuit #2 is a power-on reset for the counters. Circuit #2 works but I haven't

added #2 yet as I am concerned about a conflict since the output of both circuits will be connected to

pins 2 and 3 of each of the 74LS90 counters. Could someone please advise as to a resolution.

Thanks

I am breadboarding a frequency counter. I have attached two circuits. Circuit #1 will hopefully perform

a gate control function and circuit #2 is a power-on reset for the counters. Circuit #2 works but I haven't

added #2 yet as I am concerned about a conflict since the output of both circuits will be connected to

pins 2 and 3 of each of the 74LS90 counters. Could someone please advise as to a resolution.

Thanks

Attachments

-

833.6 KB Views: 21

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin