Hello everyone, I’m using Vishay’s Transim tool to design DC-DC converters, and during the initial configuration phase (where you set the minimum and maximum Vin, Iout, frequency, etc.), I’m asked to specify the output current that the DC-DC converter should deliver.

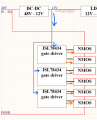

I have therefore drawn up a block diagram of the various integrated circuits that draw current on my future PCB.

The DC-DC converter in question is clearly the block on the left, and I want to know how much output current it will provide (i.e. the sum of the two blue arrows).

1) Correct me if I'm wrong, but I think the output current it will deliver is the sum of all the currents from the 'black' blocks (i.e. not the power NMOS), right?

2) If the answer is yes, in the various datasheets I look at:

2a: the maximum current at their Vdd (maximum current value)

2b: the quiescent current (minimum current value)

3) If I’ve got it right so far and I therefore calculate the maximum current as the sum of all the Imax values across the Vdd pins of the various blocks (the 2a solution) … should I enter a higher value in the simulator? (to allow for a sort of margin)

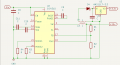

4) The LDO is linear, so its input current is equal to its output current (which is the sum of the currents from all the modules) + Iquiescent, isn't it?

I have therefore drawn up a block diagram of the various integrated circuits that draw current on my future PCB.

The DC-DC converter in question is clearly the block on the left, and I want to know how much output current it will provide (i.e. the sum of the two blue arrows).

1) Correct me if I'm wrong, but I think the output current it will deliver is the sum of all the currents from the 'black' blocks (i.e. not the power NMOS), right?

2) If the answer is yes, in the various datasheets I look at:

2a: the maximum current at their Vdd (maximum current value)

2b: the quiescent current (minimum current value)

3) If I’ve got it right so far and I therefore calculate the maximum current as the sum of all the Imax values across the Vdd pins of the various blocks (the 2a solution) … should I enter a higher value in the simulator? (to allow for a sort of margin)

4) The LDO is linear, so its input current is equal to its output current (which is the sum of the currents from all the modules) + Iquiescent, isn't it?

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin