Hello,

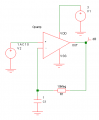

I'm trying to design an one stage OP AMP made of a differential pair, a current load and a current mirror as shown in the picture ( the first stage only, I didn't include Q7 Q6 and Compensation capacitance)

I designed the circuit to have a gain of 100V/V, a slew rate of 2V/µs, aGWB of 2.5MHz and for a load of 10pF. I followed the gm/Id methodology to size my transistors and when I plot the gain and the phase I get the following curves

Where can the problem be?

Thank you in advance for your help.

I'm trying to design an one stage OP AMP made of a differential pair, a current load and a current mirror as shown in the picture ( the first stage only, I didn't include Q7 Q6 and Compensation capacitance)

I designed the circuit to have a gain of 100V/V, a slew rate of 2V/µs, aGWB of 2.5MHz and for a load of 10pF. I followed the gm/Id methodology to size my transistors and when I plot the gain and the phase I get the following curves

Where can the problem be?

Thank you in advance for your help.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin