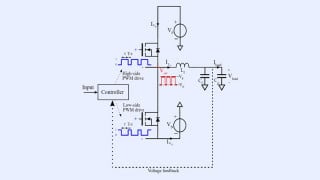

Hello, I'm trying to design a folded cascode op amp as shown below. I need a high full power bandwidth, about 90 to 100MHz, and a high gain (>60dB). I reach the required gain but it's hard for me to have a large full power BDW, it doesn't exceed the 500KHz.

From the theory, the frequency at 3db depends on the load capacitance and the output resistance of the amplifier stage. The first parameter is fixed by the load and I can't change it whereas the output resistance can be changed by changing the drain-to-source resistance of the cascode transistor. To reduce the output resistance ( and so increase f-3db), since the up and down resistance are in parallel, they need to be increased.

If I'm being correct, from the relation below, a small r01A+ small r03A + small r03 + high r01 and high r05 high should give a higher f-3db. Whenever I try to change the drain to source resistance, it either deteriorates the gain or does not increase the full power bandwidth.

Does anyone know how to increase the f-3db or have any paper/books that explain the design methodology for such architecture?

Thank you in advance for your help.

From the theory, the frequency at 3db depends on the load capacitance and the output resistance of the amplifier stage. The first parameter is fixed by the load and I can't change it whereas the output resistance can be changed by changing the drain-to-source resistance of the cascode transistor. To reduce the output resistance ( and so increase f-3db), since the up and down resistance are in parallel, they need to be increased.

If I'm being correct, from the relation below, a small r01A+ small r03A + small r03 + high r01 and high r05 high should give a higher f-3db. Whenever I try to change the drain to source resistance, it either deteriorates the gain or does not increase the full power bandwidth.

Does anyone know how to increase the f-3db or have any paper/books that explain the design methodology for such architecture?

Thank you in advance for your help.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin