Evening all,

Would you kind people be able to pick over my design and let me know if there are any issues you can foresee.

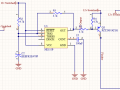

I have a motorcycle that has been badly wired with all cables and wire taps over the place. I am integrating a single 12-14V DC supply from the battery into a PCB and having it feed the lighting circuits through the handle bar switchgear.

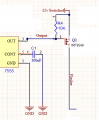

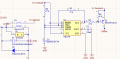

As part of this I have designed the attached Flasher circuit to supply the LED indicators, these draw around 1W front and rear. So 2W per side and grounded through the indicator itself. The indicator switch on the handle bar feeds the flasher output to the LED, so high side switching is required.

I have a 555 timer set to 50% duty cycle and a frequency of 1.5Hz, the output of which goes to the base on a PNP transistor, when the 555 is high the PNP doesn't conduct, when low the PNP is in saturation. Please ignore the Cap and resistor values in the schematic, they are just for the pcb design footprints.

The actual values are as follows.

R1 = 10K

R2 = 100K

R3 = 1K

R4 = 5.1K

C1 = 47uF

C2 = 100nF

Would there be an issue with the collector of the PNP effectively being floating unless the indicators are on and grounded?

Would you kind people be able to pick over my design and let me know if there are any issues you can foresee.

I have a motorcycle that has been badly wired with all cables and wire taps over the place. I am integrating a single 12-14V DC supply from the battery into a PCB and having it feed the lighting circuits through the handle bar switchgear.

As part of this I have designed the attached Flasher circuit to supply the LED indicators, these draw around 1W front and rear. So 2W per side and grounded through the indicator itself. The indicator switch on the handle bar feeds the flasher output to the LED, so high side switching is required.

I have a 555 timer set to 50% duty cycle and a frequency of 1.5Hz, the output of which goes to the base on a PNP transistor, when the 555 is high the PNP doesn't conduct, when low the PNP is in saturation. Please ignore the Cap and resistor values in the schematic, they are just for the pcb design footprints.

The actual values are as follows.

R1 = 10K

R2 = 100K

R3 = 1K

R4 = 5.1K

C1 = 47uF

C2 = 100nF

Would there be an issue with the collector of the PNP effectively being floating unless the indicators are on and grounded?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin