I am trying to run a LTspice simulation of this op amp I found online

http://s.eeweb.com/members/kalpana_manickavasagam/projects/2011/01/30/ASSIGNMENT-1296438312.pdf

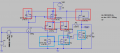

This is my LTspice simulation circuit for the above circuit

However , I get strange result compared to the result in the pdf.

AC analysis I got this.

I am trying to simulate the open loop gain and output swing of the op amp but I seem to be get wrong result.

Could anyone help me check where did I do wrongly? I have attached the ltspice file here as well - draft 1.

If anyone wants to run the simulation file , you would need to insert the 3 files (CMOS035.lib , nmos_035 and pmos_035.asy) into the ltspice folder.

CMOS035.lib in the C:\Program Files\LTC\LTspiceIV\lib\sub

nmos_035 and pmos_035.asy in the C:\Program Files\LTC\LTspiceIV\lib\sym

This the link to the CMOS035.lib , nmos_035 and pmos_035.asy files

https://www.dropbox.com/sh/0yu1pxntkl8vrpn/AAAQq7zlUU1Wsfc7W5JZgNGSa?dl=0

http://s.eeweb.com/members/kalpana_manickavasagam/projects/2011/01/30/ASSIGNMENT-1296438312.pdf

This is my LTspice simulation circuit for the above circuit

However , I get strange result compared to the result in the pdf.

AC analysis I got this.

I am trying to simulate the open loop gain and output swing of the op amp but I seem to be get wrong result.

Could anyone help me check where did I do wrongly? I have attached the ltspice file here as well - draft 1.

If anyone wants to run the simulation file , you would need to insert the 3 files (CMOS035.lib , nmos_035 and pmos_035.asy) into the ltspice folder.

CMOS035.lib in the C:\Program Files\LTC\LTspiceIV\lib\sub

nmos_035 and pmos_035.asy in the C:\Program Files\LTC\LTspiceIV\lib\sym

This the link to the CMOS035.lib , nmos_035 and pmos_035.asy files

https://www.dropbox.com/sh/0yu1pxntkl8vrpn/AAAQq7zlUU1Wsfc7W5JZgNGSa?dl=0

Attachments

-

3.2 KB Views: 9

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin