I'd appreciate it if somene could check my maths here. I'm getting confused with the units, as the numbers are small.

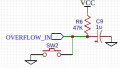

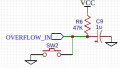

For this circuit:

I'd like to calculate the voltage at the point OVERFLOW_IN, and current consumed when SW2 is closed.

OVERFLOW_IN is a digital input on an MCU. VCC=5VDC. Is it just simple Ohms law?

When SW2 is closed, the path is simply from VCC to ground (assuming the MCU input is very high impedance). So:

I=V/R = 5 / 47,000 = 0.000106383 = 106uA.

Given 106uA, voltage drop across R6 is: 0.000106383 * 47,000 = 5V. Er... So the resistor drops the entire 5V? That's kirchhoff's law at work, yes?

So, when S2 is closed (and C9 is empty), there will be exactly 0V at OVERFLOW_IN, and current draw of 106uA. All 5V is dropped across R6, yes?

Is my reasoning correct? I'm wanting to consume as little current as possible when the switch is closed, ideally tens of microamps. So, for example, a 200K resistor would result in the same effect as above wrt to voltage (i.e. all 5V would still be dropped across R6 when SW2 is closed), but only 25uA consumed? Is that correct? I'm very sorry to post such fundamental questions, I just want to get some guidance to ensure I'm on the right track.

This is from a working circuit, but I'd like to reduce the current consumption. As noted above it's currently using 47K, which is up around 100uA. I see no reason to pull 100uA if I can pull 25.

The capacitor is there to stop bouncing. In real life, SW2 is a microswitch on a water tank and it is quite bouncy and wakes the MCU many times when switching. 'Slugging' it with the capacitor fixed that problem. I think increasing the resistor value will increase the time taken to fill the capacitor, yes? So I'll need to reduce the size of the capacitor.

I'd be grateful for any insights.

Regards

Mark

For this circuit:

I'd like to calculate the voltage at the point OVERFLOW_IN, and current consumed when SW2 is closed.

OVERFLOW_IN is a digital input on an MCU. VCC=5VDC. Is it just simple Ohms law?

When SW2 is closed, the path is simply from VCC to ground (assuming the MCU input is very high impedance). So:

I=V/R = 5 / 47,000 = 0.000106383 = 106uA.

Given 106uA, voltage drop across R6 is: 0.000106383 * 47,000 = 5V. Er... So the resistor drops the entire 5V? That's kirchhoff's law at work, yes?

So, when S2 is closed (and C9 is empty), there will be exactly 0V at OVERFLOW_IN, and current draw of 106uA. All 5V is dropped across R6, yes?

Is my reasoning correct? I'm wanting to consume as little current as possible when the switch is closed, ideally tens of microamps. So, for example, a 200K resistor would result in the same effect as above wrt to voltage (i.e. all 5V would still be dropped across R6 when SW2 is closed), but only 25uA consumed? Is that correct? I'm very sorry to post such fundamental questions, I just want to get some guidance to ensure I'm on the right track.

This is from a working circuit, but I'd like to reduce the current consumption. As noted above it's currently using 47K, which is up around 100uA. I see no reason to pull 100uA if I can pull 25.

The capacitor is there to stop bouncing. In real life, SW2 is a microswitch on a water tank and it is quite bouncy and wakes the MCU many times when switching. 'Slugging' it with the capacitor fixed that problem. I think increasing the resistor value will increase the time taken to fill the capacitor, yes? So I'll need to reduce the size of the capacitor.

I'd be grateful for any insights.

Regards

Mark

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin