Hi all,

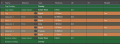

I have a 4-layer PCB with a below layer-stack and I will be having a net that is supposed to handle 100A. I know I should use a heavy copper PCB instead of this 4-layer PCB but to save cost I stitched 4 polygons on all layers with (0.5 hole size, 1 diameter) vias to accommodate the high current.

According to a conductor width calculator, the width of the conductor should be more than 10 cm for a 25 mm long trace to be able to handle that amount of current but of course that's impractical in my case so I used roughly 13 mm thick polygons in all 4 layers and stitched them together...

I even added jumper links and some pads (to be filled with solder mountain) on the external layers just in case the PCB can't handle the current.

Now, my questions are :

Is this a good idea for a <50khz, 100A signal? or is there a better approach?

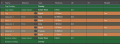

I used 1:2 and 3:4 blind vias to stitch the layers 1/2 and 3/4 together and opted not to use 2:3 buried vias to not increase the price even more...is this ok? meaning not stitching layers 2 and 3?

Thanks,

I have a 4-layer PCB with a below layer-stack and I will be having a net that is supposed to handle 100A. I know I should use a heavy copper PCB instead of this 4-layer PCB but to save cost I stitched 4 polygons on all layers with (0.5 hole size, 1 diameter) vias to accommodate the high current.

According to a conductor width calculator, the width of the conductor should be more than 10 cm for a 25 mm long trace to be able to handle that amount of current but of course that's impractical in my case so I used roughly 13 mm thick polygons in all 4 layers and stitched them together...

I even added jumper links and some pads (to be filled with solder mountain) on the external layers just in case the PCB can't handle the current.

Now, my questions are :

Is this a good idea for a <50khz, 100A signal? or is there a better approach?

I used 1:2 and 3:4 blind vias to stitch the layers 1/2 and 3/4 together and opted not to use 2:3 buried vias to not increase the price even more...is this ok? meaning not stitching layers 2 and 3?

Thanks,