Hi everyone.

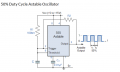

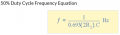

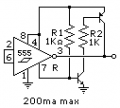

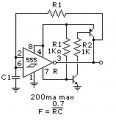

I am trying to generate a square wave signal with 50% duty cycle with the help of circuit given in https://www.electronics-tutorials.ws/waveforms/555_oscillator.html (the circuit with heading '50% Duty Cycle Astable Oscillator'). I am using C = 0.01uF and R = 10kohm (5% tolerance). According to the calculations, the generated frequency should be 7215 Hz but the frequency observed at the oscilloscope is 5.81kHz when power supplied to the timer is 8V. Can anyone tell why is this so? If anyone has an idea of a better timer circuit which can generate perfect square wave for longer duration of time, please suggest. I am using STMicroelectronics CHN NE555N KJW949 timer for it.

I am trying to generate a square wave signal with 50% duty cycle with the help of circuit given in https://www.electronics-tutorials.ws/waveforms/555_oscillator.html (the circuit with heading '50% Duty Cycle Astable Oscillator'). I am using C = 0.01uF and R = 10kohm (5% tolerance). According to the calculations, the generated frequency should be 7215 Hz but the frequency observed at the oscilloscope is 5.81kHz when power supplied to the timer is 8V. Can anyone tell why is this so? If anyone has an idea of a better timer circuit which can generate perfect square wave for longer duration of time, please suggest. I am using STMicroelectronics CHN NE555N KJW949 timer for it.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin