Implement f = A' + B'C + B'D using NAND only

- Thread starter mohireza

- Start date

Scroll to continue with content

We don't either, as you haven't posted your best attempt so far.I don't know why

Welcome to AAC!

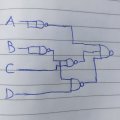

You beat me. The best I could do is six 2-input NAND gates.I have the answer which uses 5 NANDs but my professor says this circuit only needs 4 (he is skipping on the A' NAND and I don't know why)

First, you need to show your best attempt to solve your homework problem. We can then look for errors and provide hints and suggestions -- we can't just give you the answer.I have the answer which uses 5 NANDs but my professor says this circuit only needs 4 (he is skipping on the A' NAND and I don't know why)

Second, we need more details about the constraints. For instance, are you restricted to 2-input NAND gates, or are you allowed to use n-input NAND gates? Are you allowed to assume that yo have both the straight and complemented versions of the input signals available, or just the straight signals?

So, it appears that you are able to use arbitrary-input NAND gates. That's an important point, since these types of problems usually limit things to only 2-input gates.

Have you verified that your solution actually works?

We know that if ANY input to a NAND gate is LO, then the output is HI, right?

So what happens if A is HI?

That means that the output of the top NAND gate is LO, which means that the output of the final NAND gate is HI, regardless of the state of the other two inputs.

Does that behavior match the logic equation you are trying to implement?

Have you verified that your solution actually works?

We know that if ANY input to a NAND gate is LO, then the output is HI, right?

So what happens if A is HI?

That means that the output of the top NAND gate is LO, which means that the output of the final NAND gate is HI, regardless of the state of the other two inputs.

Does that behavior match the logic equation you are trying to implement?

You say that the instructor is "skipping on the A' input". That implies that you have the instructor's solution in order to know what he is or isn't skipping. What is that solution?

Have you verified that it does or does not work? Remember, all you need to show is one combination of inputs that doesn't produce the correct output and you have proven that that solution is wrong.

Have you verified that it does or does not work? Remember, all you need to show is one combination of inputs that doesn't produce the correct output and you have proven that that solution is wrong.

The TS's solution is correct... almost. You don't need the /A, but you do need A.

Original logic /A + /BC + /BD as given

The solution is 4 NAND.. The trick is not to do the obvious and start by applying DeMorgan to the /BC + /BD element as /B(C+D). That leads to a 6 gate solution with no obvious further simplification. Instead, start with /A + /BC. Actully its obvious by inspection of the 5 gate circuit of the original using general DeMorgan on the output gate, ie change OR to NAND and invert the inputs...

Original logic /A + /BC + /BD as given

The solution is 4 NAND.. The trick is not to do the obvious and start by applying DeMorgan to the /BC + /BD element as /B(C+D). That leads to a 6 gate solution with no obvious further simplification. Instead, start with /A + /BC. Actully its obvious by inspection of the 5 gate circuit of the original using general DeMorgan on the output gate, ie change OR to NAND and invert the inputs...

Beau Schwabe

- Joined Nov 7, 2019

- 186

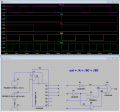

If you want to get tricky, you can do it with 3 NAND gates .... https://tinyurl.com/ynhbz5jc

The circuit in post #8 - if you read what I wrote, is the original logic statement, implemented as given, to show what the required output actually is. I haven't shown the actual 4 NAND result, but hinted as to how to get to it as I didn't want to give it away - yet!Unfortunately neither the post #8 circuit nor the post #9 circuit meets the thread title requirements.

Have you actually tested the truth table for your 5 gate solution? Does it actually give the required output?I have the answer which uses 5 NANDs but my professor says this circuit only needs 4 (he is skipping on the A' NAND and I don't know why)

I think you got the right answer except you forgot that an AND gate with negated output is the same as an OR gate with negated inputs.

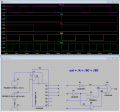

Attachments

-

1.3 MB Views: 3

Were you able to solve the circuit with a maximum of four 2-input NAND gates? It appears TS has left the building so I'd appreciate the answer. I spent quite a while trying to solve it.The circuit in post #8 - if you read what I wrote, is the original logic statement, implemented as given, to show what the required output actually is. I haven't shown the actual 4 NAND result, but hinted as to how to get to it as I didn't want to give it away - yet!

That's what happens if you try to use DeMorgan on the /BC + /BD clause first, like this, /BC + /BD = /B(C + D ) = /B/(/C/D) Call that X and do /A + X = /(A/X) = /(A/(/B/(/C/D))) which requires 5 NAND gates, three to give /B, /C, /D, one for /(/C/D),Were you able to solve the circuit with a maximum of four 2-input NAND gates? It appears TS has left the building so I'd appreciate the answer. I spent quite a while trying to solve it.

another for /(/B/(/C/D)) and the fifth for bringing in the A. I couldn't see how to simplify that to the 4 gate solution, though clearly it must be possible...

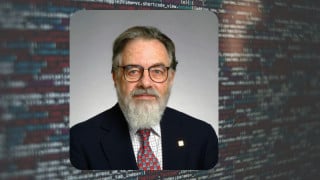

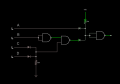

The 4 gate solution is this:

The constraint isn't 2-input NAND gates, just NAND gates, as evidenced by the TS's solution attempt, which included a 3-input gate.Were you able to solve the circuit with a maximum of four 2-input NAND gates? It appears TS has left the building so I'd appreciate the answer. I spent quite a while trying to solve it.

His solution was almost correct, but he had an additional NAND gate inverter on the A line. Removing that leaves you with a valid four NAND gate solution involving three 2-input and one 3-input gates.

As soon as you allow the use of NAND gates with more than two inputs, the solution drops out immediately by applying DeMorgan's to the original expression. This is why I asked, in my original response, whether the solution allowed the use of n-input gates.That's what happens if you try to use DeMorgan on the /BC + /BD clause first, like this, /BC + /BD = /B(C + D ) = /B/(/C/D) Call that X and do /A + X = /(A/X) = /(A/(/B/(/C/D))) which requires 5 NAND gates, three to give /B, /C, /D, one for /(/C/D),

another for /(/B/(/C/D)) and the fifth for bringing in the A. I couldn't see how to simplify that to the 4 gate solution, though clearly it must be possible...

The 4 gate solution is this:

View attachment 317640

Y = A' + B'C + B'D

Now apply DeMorgan's:

Y = ( (A')' · (B'C)' · (B'D)' )'

Y = ( A · (B'C)' · (B'D)' )'

And there you have your four-gate solution.

Using square brackets to highlight the gates:

Y = [( (A')' · [ ([ B' ]C)' ] · [ ([ B' ]D)' ] )']

Exactly, and if you construct the original logic with gates, as I did in post #8 its obvious by inspection - convert the ANDs to NANDs. remove the invert on A and replace the OR with a NAND...As soon as you allow the use of NAND gates with more than two inputs, the solution drops out immediately by applying DeMorgan's to the original expression

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin