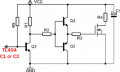

In my first attempt, a bipolar clock (-5V to +5V) gives a short-height square wave, which toggles between about 9.5V and 10V.

When i change clock to unipolar clock (0V to +5V) i get a steady 10V output.

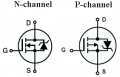

My mosfet "threshold V" defaults to -1.5V in this sim, but I can change it if needed. i want typical P-channel behavior:

0V = On

5V = Off

Based on my (obviously wrong) interpretation of

https://www.electronics-tutorials.ws/transistor/tran_7.html

The middle R represent my load.

You can play with the sim here. http://tinyurl.com/y7bv7kye

A simpler attempt. Again, unipolar 5V square give flatline output.

sim: http://tinyurl.com/y7l38mo6

Thx

When i change clock to unipolar clock (0V to +5V) i get a steady 10V output.

My mosfet "threshold V" defaults to -1.5V in this sim, but I can change it if needed. i want typical P-channel behavior:

0V = On

5V = Off

Based on my (obviously wrong) interpretation of

https://www.electronics-tutorials.ws/transistor/tran_7.html

The middle R represent my load.

You can play with the sim here. http://tinyurl.com/y7bv7kye

A simpler attempt. Again, unipolar 5V square give flatline output.

sim: http://tinyurl.com/y7l38mo6

Thx

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin