How to make simple 4 Latching switch that only turns on only one at a time.

- Thread starter BLiND18514

- Start date

Scroll to continue with content

They are called "radio buttons". I've done them with relays...what a pain. Googled: radio button circuit

Found this: http://www.simplecircuitdiagram.com/2399-radio-buttons-using-push-on-switch-latching-circuit/

Didn't see any with 555s.

Ken

Found this: http://www.simplecircuitdiagram.com/2399-radio-buttons-using-push-on-switch-latching-circuit/

Didn't see any with 555s.

Ken

Thanks for the circuits guys! I think I should now move on towards 555 chip since using micro controller or even logic ics is much better and easier.

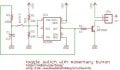

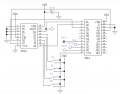

From another thread. I've used variations of this circuit for many years. Only one input switch and output driver are shown. You might not need the output FET in your application. BTW, what is your application? U1 Vdd and Vss connections not shown by convention.

Note - this circuit does not have explicit exclusivity logic. However, the 574 is edge-triggered, so it should capture only the first signal in a close call. As long as one button is pressed, all others are locked out. Recovery time between buttons is about 0.2 sec. You can adjust this by changing C1.

EDIT: Wrong schematic. Wally caught it.

ak

Note - this circuit does not have explicit exclusivity logic. However, the 574 is edge-triggered, so it should capture only the first signal in a close call. As long as one button is pressed, all others are locked out. Recovery time between buttons is about 0.2 sec. You can adjust this by changing C1.

EDIT: Wrong schematic. Wally caught it.

ak

Last edited:

Really?I've used variations of this circuit for many years.

In that circuit all the inputs, except the PB input, follow the clock voltage through their 10k resistors, so you are depending upon the clock triggering before those inputs reach a logic one, which seems dicey.

I would not expect that to reliably happen.

A resistor, say 10k on each input to ground using another RN1 array, would prevent that from being a problem.

How does that occur?As long as one button is pressed, all others are locked out.

It is an edge-triggered latch. Holding a button holds the clock input high.How does that occur?

ak

Okay.It is an edge-triggered latch. Holding a button holds the clock input high.

That works if the second button is pressed after the clock has already gone high.

How about adding an NPN to drive the PNP?There is a way around that, so I'll take one more swing.

Yeah, the sch is 1/2 modified, but I'm getting some outside work done in the sun. more later. If the output polarity is nor required to go high, then there is no reason to add the second Q.How about adding an NPN to drive the PNP?

ak

I agree.If you are sure only one button will be pressed at a time, you might get away with deleting C1.

With the high collector and drain resistor values, there should be enough delay in the clock signal due to stray capacitances to satisfy the D input setup time.

But my preference though would be to stay with the PNP you originally had to drive the clock, as that gives a faster clock rise-time, with less chance of a slow clock rise causing problems with the flip-flop operation.

Some edge-triggered flip-flops are sensitive to clock rise-time, although I'm not sure if this one is.

Last edited:

In sch 12, the PNP is driving the clock through a 9K - 2.2 uF time constant. In sch 16, the NPN tries to dead short a much smaller capacitor with no resistor in series, and the resulting (much faster) ramp is steepened more by the gain of the FET. You can decrease R2 for even more dv/dt.

ak

ak

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin