A ckt to clamp a signal of 1.67to-1.67v to 3.3to0v. Signal is about 50kS/s. I needed to implement this practically so that i can give input to adc of a microcontroller. So the signal accuracy is crucial.

How to do active clamping?

- Thread starter raisal_salim

- Start date

Scroll to continue with content

Quick question...A ckt to clamp a signal of 1.67to-1.67v to 3.3to0v. Signal is about 50kS/s. I needed to implement this practically so that i can give input to adc of a microcontroller. So the signal accuracy is crucial.

Are you talking about a level converter circuit? That sounds more like what you are after but I'll wait for your reply.

A clamp circuit usually acts as a limiter that limits the signal to some max or min value.

That circuit is AC coupled, so you will lose any information about the DC level.View attachment 329367i found something like this. But don't know about the values needed to be given

What accuracy?So the signal accuracy is crucial.

How many bits is the A/D converter?

Is the reference voltage for the A/D available?

ronsimpson

- Joined Oct 7, 2019

- 4,653

16-bit adc. Im thinking vdda 3.3 vssa gndWhat accuracy?

How many bits is the A/D converter?

Is the reference voltage for the A/D available?

Yes, a level shifterQuick question...

Are you talking about a level converter circuit? That sounds more like what you are after but I'll wait for your reply.

A clamp circuit usually acts as a limiter that limits the signal to some max or min value.

But do you need a DC level shifter, or are you just interested in the AC component of the signal?Yes, a level shifter

16-bit adc. Im thinking vdda 3.3 vssa gnd

Getting 16-bit accuracy (0.0015%) in a level shifter is not trivial.Yes, a level shifter

What accuracy does your signal really require?

Is it just 16-bit resolution, with some lower accuracy (say 1% or perhaps better).

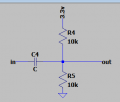

Hi,This circuit takes the signal and centers it at 1/2 of the supply voltage. This is good for ADC looking at a AC signal.

View attachment 329397

That looks like it could work except for the DC offset and drift. R4 and R5 might have to be lowered in value, as low as 2k each but I doubt any lower than that. The value of the capacitor would have to be large enough to keep the attenuation down also at the lowest frequency.

I am guessing that the accuracy does not have to be too high because 1.67+1.67 does not equal 3.3Getting 16-bit accuracy (0.0015%) in a level shifter is not trivial.

What accuracy does your signal really require?

Is it just 16-bit resolution, with some lower accuracy (say 1% or perhaps better).

Did you mean that it might be rectified instead of having the DC offset shifted?But do you need a DC level shifter, or are you just interested in the AC component of the signal?

ronsimpson

- Joined Oct 7, 2019

- 4,653

I don't know enough about what is being measured.

I don't understand the word clamping?

Do you need to measure DC? If so, there will be no capacitors. Just add (3.3v/2) to the signal. Problem is that 1.65V may not be 1/2 of the supply voltage.

If AC only then see post #8.

Is the wave form sign wave like the power line? Or is it complex?

I don't understand the word clamping?

What frequency?A ckt to clamp a signal of 1.67to-1.67v to 3.3to0v.

Do you need to measure DC? If so, there will be no capacitors. Just add (3.3v/2) to the signal. Problem is that 1.65V may not be 1/2 of the supply voltage.

If AC only then see post #8.

Is the wave form sign wave like the power line? Or is it complex?

Just wondering what the TS wants to know about the signal. It's a 50kHz signal of some kind, but suppose it was PWM - if so the average DC level would vary with the PWM ratio on the side that is capacitively coupled.Did you mean that it might be rectified instead of having the DC offset shifted?

ronsimpson

- Joined Oct 7, 2019

- 4,653

I think the ADC will sample at 50khz.the signal. It's a 50kHz signal of some kind

Nyquist says that it will have to sample at more than 100kHzI think the ADC will sample at 50khz.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin