How do I make a 74LS192 decade counter run 1 cycle and stop?

- Thread starter jus.2ne

- Start date

Scroll to continue with content

Welcome to AAC!

Is this schoolwork?

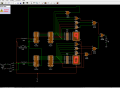

EDIT: This less colorful schematic might be easier for members to read:

We don't put text on top of symbols or wires. You can't do anything about the corny curved wires or the unnecessary logic level indications where pin numbers would be more helpful. Since the simulator supports resistors, you should use one for the LED.

Is this schoolwork?

EDIT: This less colorful schematic might be easier for members to read:

We don't put text on top of symbols or wires. You can't do anything about the corny curved wires or the unnecessary logic level indications where pin numbers would be more helpful. Since the simulator supports resistors, you should use one for the LED.

Last edited:

You have two choices, count to n and recycle which is what you are doing or count to n and halt which is what I assume you want. Normally you would run your clock through a NAND gate like a 7400 where one input is your clock and the other goes to n. See page 62 of this link for a schematic to work from and give you the idea.

Ron

Ron

Hello! Nope, this isn't schoolwork, just a hobbyistWelcome to AAC!

Is this schoolwork?

EDIT: This less colorful schematic might be easier for members to read:

View attachment 279377

We don't put text on top of symbols or wires. You can't do anything about the corny curved wires or the unnecessary logic level indications where pin numbers would be more helpful. Since the simulator supports resistors, you should use one for the LED.

Thanks for your feedback on my first post!

Just exactly what I need! I've been looking at different articles for a while now. Going to post the result once I get it done. Huge thanks!You have two choices, count to n and recycle which is what you are doing or count to n and halt which is what I assume you want. Normally you would run your clock through a NAND gate like a 7400 where one input is your clock and the other goes to n. See page 62 of this link for a schematic to work from and give you the idea.

Ron

No problem and by all means any further questions just ask.Just exactly what I need! I've been looking at different articles for a while now. Going to post the result once I get it done. Huge thanks!

Ron

Nope, this isn't schoolwork, just a hobbyist

- What is the purpose of decoding the segment outputs of the LS47's instead of the counter outputs?

- When switches are opened, you're allowing inputs to float.

- Is this supposed to be a 2 digit counter? Why do you have independent clocks to the counters?

- You have too many floating inputs.

- What count do you want the counter to stop at? The decode logic on the upper counter will decode 0 or 8.

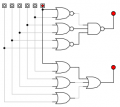

For most circuits, I find not using NOR and NAND gates easier to read.

If you apply De Morgan's law to the NAND gate, you get the lower equivalent which I find much easier to comprehend.

If you were really doing an AND function, using a NAND would make sense, but you're implementing an OR function, so using OR gates would make more sense.

If you apply De Morgan's law to the NAND gate, you get the lower equivalent which I find much easier to comprehend.

If you were really doing an AND function, using a NAND would make sense, but you're implementing an OR function, so using OR gates would make more sense.

Though keep in mind that the lower circuit will have a greater propagation delay and consume more power (assuming that we are talking about a CMOS implementation). If neither of those factors matter, then going with an implementation that is more intuitively obvious to people reading the schematic has a lot of merit. Also, since the 4000 series gates buffer both the input and the output, this generic delay/speed penalty is a lot murkier.For most circuits, I find not using NOR and NAND gates easier to read.

If you apply De Morgan's law to the NAND gate, you get the lower equivalent which I find much easier to comprehend.

View attachment 279436

If you were really doing an AND function, using a NAND would make sense, but you're implementing an OR function, so using OR gates would make more sense.

I notice that the schematic is mixing 74LS TTL parts and 4000 CMOS. Care must be taken that the I/O voltage levels and drive strengths are compatible. It's been years since I've looked at that, so I don't know the answer off the top of my head.

For most circuits, I find not using NOR and NAND gates easier to read.

If you apply De Morgan's law to the NAND gate, you get the lower equivalent which I find much easier to comprehend.

View attachment 279436

If you were really doing an AND function, using a NAND would make sense, but you're implementing an OR function, so using OR gates would make more sense.

Hello, I've come up with a solution to the problem with the material you sent me (the pdf one). Thank you for the advice! I used a three input AND gate whose output activates/ deactivates a Relay connected to the clock. Now, when the counter reaches 0, it halts. Thank you very much!

Attachments

-

28.7 KB Views: 20

| Thread starter | Similar threads | Forum | Replies | Date |

|---|---|---|---|---|

| D | Cascading 74LS192 | Homework Help | 2 | |

|

|

[Proteus to Breadboard] 74LS192 Decade Counter problem, ABCD output always at 1 | Homework Help | 5 | |

| A | Digital Clock using 74LS192 | Homework Help | 11 | |

| Y | 74LS192 counter problem | Digital Design | 6 | |

| R | 74ls192 circuit with relays resets display help | Digital Design | 16 |

You May Also Like

-

Keysight Introduces First Integrated Toolset for Quantum System Design

by Duane Benson

-

ISSCC 2024: Samsung Doubles DDR5 Capacity With Symmetric-Mosaic Architecture

by Duane Benson

-

Microchip Expands Its Serial SRAM Devices to 2 Mb and 4 Mb

by Jake Hertz

-

New Processors Shine on the Embedded World Stage

by Jake Hertz