Hello,

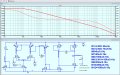

I am currently working on three stage amplifier design load of 10nF capacitor, and I am asked to find the voltage gain > 80dB, phase margin 60-80deg, power consumption < 130uW, Slew Rate ≥ 4/s and also bandwidth (unity gain) >1.2MHz.

I am getting gain of 50dB and phase margin 91degree, How can I increase my gain and fulfil the above requirement.

M1 & M2= 80u/4u

M3 & M4= 70u/0.6u

M5=5u/0.19u

M7=50u/0.19u

M8=1000u/0.18u

M6 & M11=100u/0.18u

M9=200u/0.18u

M10=980u/0.19u

M12=1000u/0.19u

I am currently working on three stage amplifier design load of 10nF capacitor, and I am asked to find the voltage gain > 80dB, phase margin 60-80deg, power consumption < 130uW, Slew Rate ≥ 4/s and also bandwidth (unity gain) >1.2MHz.

I am getting gain of 50dB and phase margin 91degree, How can I increase my gain and fulfil the above requirement.

M1 & M2= 80u/4u

M3 & M4= 70u/0.6u

M5=5u/0.19u

M7=50u/0.19u

M8=1000u/0.18u

M6 & M11=100u/0.18u

M9=200u/0.18u

M10=980u/0.19u

M12=1000u/0.19u

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin