Hello I would like to realise an oscillator that generates a CK signal with a frequency of 1kHz and Duty Cycle 30%, I can use a NE555. Because I wanted to realise it as a stable vibrator, but among the specifications I read CheDuty cycle = tH / period > 50%

Help for Oscillator that generates a CK signal with a frequency of 1kHz and Duty Cycle 30%

- Thread starter monika.duccoli

- Start date

Scroll to continue with content

Dave Lowther

- Joined Sep 8, 2016

- 332

another alternative was that I could use was the 74HC04 chip

but it seems simpler to me to use NE555 with some modifications

but it seems simpler to me to use NE555 with some modifications

What are your limits of error? How close to 1kHz does it need to be? How close to 30% duty cycle?

You would have to pay a lot of money for the capacitor if you want ±1%. it would be cheaper to use a crystal oscillator and divide it down.

However, if ±10% is good enough, then the 555 will do the job.

You would have to pay a lot of money for the capacitor if you want ±1%. it would be cheaper to use a crystal oscillator and divide it down.

However, if ±10% is good enough, then the 555 will do the job.

schmitt trigger

- Joined Jul 12, 2010

- 2,032

Crut’s suggestion should be the easiest to implement.

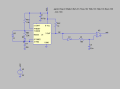

Now I try to do the simulation with a duty cycle of 70% and then use an inverting, after having created an oscillator that generates a CK signal with a frequency of 1kHz and Duty Cycle 30% I have to proceed with a circuit that for each rising edge of the signal CK output from the oscillator generates a negative pulse (1) with duration Tw1=25µs after a delay time TEL=125µs.

To create this circuit I had thought of first using a capacitance obtaining a delay time equal to 125µs and then using the OR, I sized the resistance and the capacitance in such a way as to have a pulse duration equal to 25µs

Do you think this could be a good idea?

To create this circuit I had thought of first using a capacitance obtaining a delay time equal to 125µs and then using the OR, I sized the resistance and the capacitance in such a way as to have a pulse duration equal to 25µs

Do you think this could be a good idea?

Ho una tolleranza +/- 5% sulla frequenza di oscillazione e sulla durata degli impulsi.What are your limits of error? How close to 1kHz does it need to be? How close to 30% duty cycle?

You would have to pay a lot of money for the capacitor if you want ±1%. it would be cheaper to use a crystal oscillator and divide it down.

However, if ±10% is good enough, then the 555 will do the job.

Mod translate, please use English text.

I have a +/- 5% tolerance on the oscillation frequency and pulse duration.

Last edited by a moderator:

That will work, but it would work (and the duty cycle would be more accurate) without A1, A2,R1 and C5.

The accuracy of the threshold voltage on a logic gate is not good. You would not achieve your 5% accuracy.Now I try to do the simulation with a duty cycle of 70% and then use an inverting, after having created an oscillator that generates a CK signal with a frequency of 1kHz and Duty Cycle 30% I have to proceed with a circuit that for each rising edge of the signal CK output from the oscillator generates a negative pulse (1) with duration Tw1=25µs after a delay time TEL=125µs.

To create this circuit I had thought of first using a capacitance obtaining a delay time equal to 125µs and then using the OR, I sized the resistance and the capacitance in such a way as to have a pulse duration equal to 25µs

Do you think this could be a good idea?

The tolerance on the threshold voltages of a 555 is ±6%, even with 1% tolerance capacitors and resistors you would not achieve your target without a preset to adjust the tiMing.Ho una tolleranza +/- 5% sulla frequenza di oscillazione e sulla durata degli impulsi.

Mod translate, please use English text.

I have a +/- 5% tolerance on the oscillation frequency and pulse duration.

I imagine but after realizing a negative pulse lasting 25µs then I need the second circuitThat will work, but it would work (and the duty cycle would be more accurate) without A1, A2,R1 and C5.

so you recommend adding a trimmer (adjustable potentiometer) to your setup. This allows you to manually calibrate the frequency and duty cycle. You can use a trimmer to adjust the resistance in the circuit to get the specifications you want?The tolerance on the threshold voltages of a 555 is ±6%, even with 1% tolerance capacitors and resistors you would not achieve your target without a preset to adjust the tiMing.

I have to create an oscillator that generates a CK signal with a frequency of 1kHz and Duty Cycle 30% and a circuit that for each rising edge of the CK signal output from the oscillator generates a negative pulse (1) of duration

Tw1=25μs after a delay time TEL=125μs. Assume a tolerance of +/- 5% on the oscillation frequency and pulse duration.

to obtain a timed delay of 125µs I thought of using a monostable 555, but it seems too expensive to me, I wanted to use something simpler

Tw1=25μs after a delay time TEL=125μs. Assume a tolerance of +/- 5% on the oscillation frequency and pulse duration.

to obtain a timed delay of 125µs I thought of using a monostable 555, but it seems too expensive to me, I wanted to use something simpler

Don't understand why you need a 30% duty-cycle of a 1kHz signal if you are generating such short pulses.have to create an oscillator that generates a CK signal with a frequency of 1kHz and Duty Cycle 30% and a circuit that for each rising edge of the CK signal output from the oscillator generates a negative pulse (1) of duration

Tw1=25μs after a delay time TEL=125μs. Assume a tolerance of +/- 5% on the oscillation frequency and pulse duration.

to obtain a timed delay of 125µs

What does the duty-cycle have to do with anything?

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin