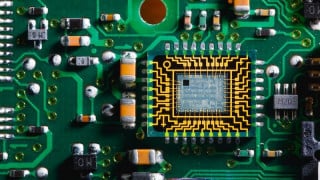

Hello I am trying to implement the circuit bellow.

as i see it there is no way to supply both DC and AC on a simple 1 substrate 2 metal layer device because the RC connected to the opamps.

So i cannot connect -Vs and +Vs on the same layer, so i will do a VIA to M3 and draw there a trance and then another VIA from M3 to M1 +VS node.

but the M3 power supply layer also needs a ground, so should i use M4 as the ground for M3 and connect M4 and M2 grounds together with a VIA?

Does that makes any logical pcb design sense? or is there other alternative?

Thanks.

as i see it there is no way to supply both DC and AC on a simple 1 substrate 2 metal layer device because the RC connected to the opamps.

So i cannot connect -Vs and +Vs on the same layer, so i will do a VIA to M3 and draw there a trance and then another VIA from M3 to M1 +VS node.

but the M3 power supply layer also needs a ground, so should i use M4 as the ground for M3 and connect M4 and M2 grounds together with a VIA?

Does that makes any logical pcb design sense? or is there other alternative?

Thanks.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin