Hi there,

I have been working on this for a few days now and am kind of stuck, so I have decided to reach out to the community to see if anyone can shed some light on my doubts regarding the following circuit.

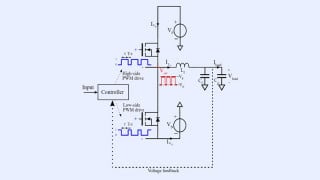

The circuit I have drawn is based on the reference design for the CS5530 provided by Cirrus Logic.

I aim to design a loadcell (Wheatstone bridge) weigh indicator capable of reading 40000 intervals, where the transducer allows it).

Although it will not be used to read 40000 intervals, I would like to set that as the target for the project.

So far, this is what I have been able to draw:

In the schematic above, I have kept the digital voltage separate from the analog voltage as per the Cirrus schematic.

I will list all my doubts, even though I do not expect all of them to be answered, to avoid creating multiple repetitive posts.

My doubts are as follows:

1. How can I supply VD+ and VA+? Can they be the same 3V3 or 5V rail coming from an LDO?

2. From the schematic, it is possible to see that Vref from the LT1019 is 2.5V; would it not be better to use the 5V version of the LT1019 to create a 5V excitation for the bridge?

3. In the schematic above, I have kept the digital voltage separate from the analog voltage as per the Cirrus schematic although I was wondering if can VD- and VA- be tied to the same ground plane?

I am new to this, so I apologise if something is missing or unclear; any help will be greatly appreciated!

I have been working on this for a few days now and am kind of stuck, so I have decided to reach out to the community to see if anyone can shed some light on my doubts regarding the following circuit.

The circuit I have drawn is based on the reference design for the CS5530 provided by Cirrus Logic.

I aim to design a loadcell (Wheatstone bridge) weigh indicator capable of reading 40000 intervals, where the transducer allows it).

Although it will not be used to read 40000 intervals, I would like to set that as the target for the project.

So far, this is what I have been able to draw:

In the schematic above, I have kept the digital voltage separate from the analog voltage as per the Cirrus schematic.

I will list all my doubts, even though I do not expect all of them to be answered, to avoid creating multiple repetitive posts.

My doubts are as follows:

1. How can I supply VD+ and VA+? Can they be the same 3V3 or 5V rail coming from an LDO?

2. From the schematic, it is possible to see that Vref from the LT1019 is 2.5V; would it not be better to use the 5V version of the LT1019 to create a 5V excitation for the bridge?

3. In the schematic above, I have kept the digital voltage separate from the analog voltage as per the Cirrus schematic although I was wondering if can VD- and VA- be tied to the same ground plane?

I am new to this, so I apologise if something is missing or unclear; any help will be greatly appreciated!

Attachments

-

56.1 KB Views: 4

-

55.4 KB Views: 4

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin