Sorry if this has been answered before, I've already tried searching the forum and haven't been able to find anything yet.

If I chain 6 j/k flipflops together and use something like a 4 input nand gate I can construct a mod-60 counter that will take for example a 60hz input and provide a 1hz output.

What I'm trying to achieve is after it hits 60 and the output flips have it immediately reset on the next clock input pulse.

I.e. one state for 1hz opposite state for only 1/60hz. etc.

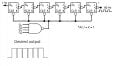

i attach a picture of my overall design idea which should produce an even 1hz on / off output and a mock waveform of the desired output I wish to achieve.

Any pointers or advice would be greatly appreciated. Perhaps I can combine the nand with the clock signal and reset it that way but it has been many years since i've worked with logic gates and this is just a curiosity project that came about as a result of finding a box full of old logic chips while having a clearout.

Kind Regards.

If I chain 6 j/k flipflops together and use something like a 4 input nand gate I can construct a mod-60 counter that will take for example a 60hz input and provide a 1hz output.

What I'm trying to achieve is after it hits 60 and the output flips have it immediately reset on the next clock input pulse.

I.e. one state for 1hz opposite state for only 1/60hz. etc.

i attach a picture of my overall design idea which should produce an even 1hz on / off output and a mock waveform of the desired output I wish to achieve.

Any pointers or advice would be greatly appreciated. Perhaps I can combine the nand with the clock signal and reset it that way but it has been many years since i've worked with logic gates and this is just a curiosity project that came about as a result of finding a box full of old logic chips while having a clearout.

Kind Regards.

Attachments

-

77.7 KB Views: 18

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin