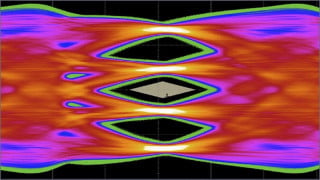

Hello, I am trying to build this circuit on a breadboard. I encountered a problem where the minute counter wont work if the first digit (M0) is 0. However, it counts normally from 1, 2, …, 9, 0 every time it finishes counting 60 seconds. Once it returns to 0, it wont count to 1. Is it possible that this is a problem with the current output of the 74ls08? I’ve checked the breadboard connections and tested the ICs separately. How can I fix this?

p.s. I used an Arduino as a voltage source and 1hz clock supply

p.s. I used an Arduino as a voltage source and 1hz clock supply

Attachments

-

99.7 KB Views: 38

-

660.4 KB Views: 34

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin