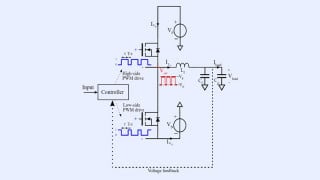

I have always placed a decoupling cap on my VDD pin as close to the pin as possible. But I was looking over the datasheet for my pic and noticed this:

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS

Exactly what does that mean? Do I really need a decoupling cap on VSS? How would that work exactly? Would I tie it to ground? That does not seem to make much sense to me since I would be basically shorting out the cap. Would I tie is it to VSS?

Or does is simply mean I need a 1 cap on the VDD pin just like I have been doing?

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS

Exactly what does that mean? Do I really need a decoupling cap on VSS? How would that work exactly? Would I tie it to ground? That does not seem to make much sense to me since I would be basically shorting out the cap. Would I tie is it to VSS?

Or does is simply mean I need a 1 cap on the VDD pin just like I have been doing?

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin