Hi,

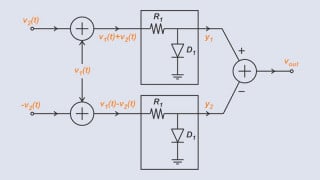

I have a large capacitance requirement on my rectifiers to achieve a certain voltage ripple, which requires 32 MLCC's. I want to use both sides of the PCB to connect the MLCC's in a more power dense way. What is the correct way to achieve this? The switching frequency of my rectifier is in the 200-500kHz range, which may complicate things. The voltage across the capacitors is also around 400VDC for each MLCC.

Is using multiple vias connected to the sides of the MLCC's and then using tracks to connect them OK? Is there a better way?

Best,

SiC

I have a large capacitance requirement on my rectifiers to achieve a certain voltage ripple, which requires 32 MLCC's. I want to use both sides of the PCB to connect the MLCC's in a more power dense way. What is the correct way to achieve this? The switching frequency of my rectifier is in the 200-500kHz range, which may complicate things. The voltage across the capacitors is also around 400VDC for each MLCC.

Is using multiple vias connected to the sides of the MLCC's and then using tracks to connect them OK? Is there a better way?

Best,

SiC

Attachments

-

592.4 KB Views: 29

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin