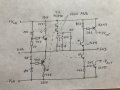

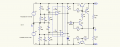

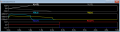

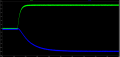

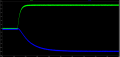

Hello , I have a power supply which outputs +12V -12V as shown below in the CSV csources and plots.I get stable 12V -12V after a second

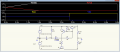

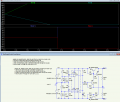

Is there a way to take the voltage after its being stable and make a pulse as shown below(or close to it) after 5seconds or so?(automatickly without using MCU)

Or atleast when the "device recognises we have 12V and -12V stable then it releases them at once(not like the power suplly does it)?

Thanks.

Is there a way to take the voltage after its being stable and make a pulse as shown below(or close to it) after 5seconds or so?(automatickly without using MCU)

Or atleast when the "device recognises we have 12V and -12V stable then it releases them at once(not like the power suplly does it)?

Thanks.

Attachments

-

3.1 MB Views: 1

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin