Hey all,

I was pondering, as I am prone to do, about JFETs and source follower circuits. More specifically, I was wondering about the Vgs vs Id chart, and the value of Vgs over one full input cycle. Here's what I'm getting at: If there's a JFET with say, Vgs(off) of -4.5V, and an Idss of 5mA, and I use it to create a source follower biased roughly @Idss, what happens to Vgs as the voltage swings up (let's say +/-8V swings, with +/-10V supply) since now the source resistor will be sinking significantly more than Idss, which, I was previously under the impression, is (nearly) the max current allowed by the JFET?

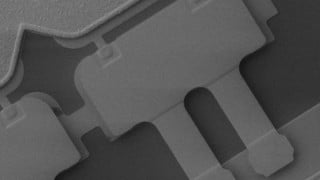

Circuit, with results of simulation (JFET is 2N5484):

If you'd like to follow along with the simulation results, the red trace is the current through the JFET, the blue trace is the input, the green trace is the output at the source, and the teal (unfortunately close to the green color) is the value of Vgs over the cycle.

From the datasheet of the 2n5484, the Idss:

So judging by the curves of the teal trace - the value of Vgs - I can tell that it really doesn't want to go above around 0.8V. This is the voltage I feel as though the JFET will still allow more current, and represents that "max current" as opposed to the "slightly less than max" Idss. This would seem, then, to be showing some sort of saturation state where the JFET can pass as much current as necessary? The current obviously goes to over 21mA, far above Idss.

I think what it comes down to is I don't fully understand what happens when you make Vgs positive, and I've been missing that detail any time I've been reading about JFETs. Could anyone help me understand this phenomenon?

Thanks in advance!

Sam Gallagher

I was pondering, as I am prone to do, about JFETs and source follower circuits. More specifically, I was wondering about the Vgs vs Id chart, and the value of Vgs over one full input cycle. Here's what I'm getting at: If there's a JFET with say, Vgs(off) of -4.5V, and an Idss of 5mA, and I use it to create a source follower biased roughly @Idss, what happens to Vgs as the voltage swings up (let's say +/-8V swings, with +/-10V supply) since now the source resistor will be sinking significantly more than Idss, which, I was previously under the impression, is (nearly) the max current allowed by the JFET?

Circuit, with results of simulation (JFET is 2N5484):

If you'd like to follow along with the simulation results, the red trace is the current through the JFET, the blue trace is the input, the green trace is the output at the source, and the teal (unfortunately close to the green color) is the value of Vgs over the cycle.

From the datasheet of the 2n5484, the Idss:

So judging by the curves of the teal trace - the value of Vgs - I can tell that it really doesn't want to go above around 0.8V. This is the voltage I feel as though the JFET will still allow more current, and represents that "max current" as opposed to the "slightly less than max" Idss. This would seem, then, to be showing some sort of saturation state where the JFET can pass as much current as necessary? The current obviously goes to over 21mA, far above Idss.

I think what it comes down to is I don't fully understand what happens when you make Vgs positive, and I've been missing that detail any time I've been reading about JFETs. Could anyone help me understand this phenomenon?

Thanks in advance!

Sam Gallagher

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin