Hello, its me once again.

I came up with another circuit, which im trying to simulate in order to keep learning.

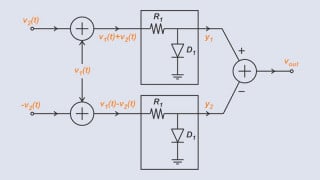

I made this circuit that has 4 transistors, 2 npn and 2 pnp.

What i expect from this circuit is the the input sine wave.

From what i understood the circuit below should work like this: i apply a sine wave to a npn and pnp transistors, what happens is that the transistors npn ( which is called Q1 in the schematic ) will shift down the signal by 0.7 ( this is what i see on emitter )

the same sine wave gets shifted up by the pnp transistor on its emitter ( which is called Q2 on the schematic )

At this point, the signal at the emitter of the npn transistor is given into the base of the second PNP ( which is called Q4 ), what the second pnp does it shifting it up again by 0.7 ( 0.7 is an approximation, lets say thats the drop on the diode), in this way u cancel the previous offset given by the npn, same thing work for the pair Q2 / Q3.

Now my questions are:

1)Is this the correct way to analyze this circuit? i got it well or i misunderstood? and if so then how it works?

2)Why the simulation shows that on its output, the signal goes from -4.5 to 4.5V? ( sine wave is 9V amplitude)

Thanks.

I came up with another circuit, which im trying to simulate in order to keep learning.

I made this circuit that has 4 transistors, 2 npn and 2 pnp.

What i expect from this circuit is the the input sine wave.

From what i understood the circuit below should work like this: i apply a sine wave to a npn and pnp transistors, what happens is that the transistors npn ( which is called Q1 in the schematic ) will shift down the signal by 0.7 ( this is what i see on emitter )

the same sine wave gets shifted up by the pnp transistor on its emitter ( which is called Q2 on the schematic )

At this point, the signal at the emitter of the npn transistor is given into the base of the second PNP ( which is called Q4 ), what the second pnp does it shifting it up again by 0.7 ( 0.7 is an approximation, lets say thats the drop on the diode), in this way u cancel the previous offset given by the npn, same thing work for the pair Q2 / Q3.

Now my questions are:

1)Is this the correct way to analyze this circuit? i got it well or i misunderstood? and if so then how it works?

2)Why the simulation shows that on its output, the signal goes from -4.5 to 4.5V? ( sine wave is 9V amplitude)

Thanks.

Attachments

-

2.3 KB Views: 1

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin