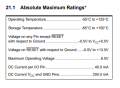

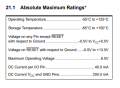

Hi, while reading the ATTiny datasheet, I came across a note I would like clarification on. According to the datasheet, max current per I/O pin and Vcc/GND pins is shown below:

However under Electrical Characters there are these notes:

" 4. Although each I/O port can sink more than the test conditions (10 mA at VCC = 5V, 5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed: 1] The sum of all IOL, for all ports, should not exceed 60 mA. If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

5. Although each I/O port can source more than the test conditions (10 mA at VCC = 5V, 5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed: 1] The sum of all IOH, for all ports, should not exceed 60 mA. If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition. "

What exactly is 'port' referring to? How do notes #4 and #5 relate to the maximum ratings? In other words, what is likely to happen if current exceeds 60mA? For example, pins 0 & 1 each sink 40mA for a total of 80mA for 10 minutes.

I can include a schematic if necessary.

Regards,

Mark

However under Electrical Characters there are these notes:

" 4. Although each I/O port can sink more than the test conditions (10 mA at VCC = 5V, 5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed: 1] The sum of all IOL, for all ports, should not exceed 60 mA. If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

5. Although each I/O port can source more than the test conditions (10 mA at VCC = 5V, 5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed: 1] The sum of all IOH, for all ports, should not exceed 60 mA. If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition. "

What exactly is 'port' referring to? How do notes #4 and #5 relate to the maximum ratings? In other words, what is likely to happen if current exceeds 60mA? For example, pins 0 & 1 each sink 40mA for a total of 80mA for 10 minutes.

I can include a schematic if necessary.

Regards,

Mark

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin