Why there is an initial peaking at the instrumentation amplifier output

- Thread starter hoyyoth

- Start date

Scroll to continue with content

Fomr me it is working.

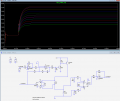

My concern is the initial peaking shown in green

My concern is the initial peaking shown in green

Attachments

-

128 KB Views: 113

Last edited:

I replaced all athe ADI parts with equivalent TI Parts.Lot of ringing at the output.Can you please check the attached file.

Attachments

-

6.2 KB Views: 7

Sorry, I don't have those TI models and don't want to install them.I replaced all athe ADI parts with equivalent TI Parts.Lot of ringing at the output.Can you please check the attached file.

Ringing could indicate a feedback loop instability.

Trace the signal through the circuit and see if you can determine its starting point.

Last edited:

RPLaJeunesse

- Joined Jul 29, 2018

- 262

With no emitter resistors Q1 and Q2 have a lot of voltage gain in the loop. I would add emitter resistors to both such that the conversion of Q1 base voltage to Q2 collector current is much more predictable and linear. As needed add loop gain by adding gain to U2 via boosting R4. I'm also wondering if a series RC from Q2 collector to U2 - input might also help kill oscillation.

MisterBill2

- Joined Jan 23, 2018

- 27,387

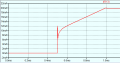

Quite a constant current regulator circuit for the PT100 sensor. Of course there will be a spike until the capacitors charge up in the PT100 current supply.

Hi,

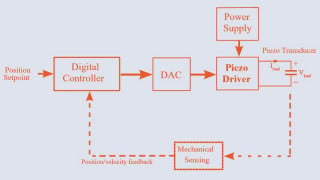

I am attaching the simulation file of one of my circuit.It consists of many opamps and BJT's. I know how to check the stability of this circuit(I know it for single opamp circuits).

My input is V3(I_PT100_SET) and output is I_PT100_ACT .

Below is the output waveform.I can see some ringing initially.Can you please help me to compensate it.

I am attaching the simulation file of one of my circuit.It consists of many opamps and BJT's. I know how to check the stability of this circuit(I know it for single opamp circuits).

My input is V3(I_PT100_SET) and output is I_PT100_ACT .

Below is the output waveform.I can see some ringing initially.Can you please help me to compensate it.

Attachments

-

6.3 KB Views: 6

May I know How do I design resistors.With no emitter resistors Q1 and Q2 have a lot of voltage gain in the loop. I would add emitter resistors to both such that the conversion of Q1 base voltage to Q2 collector current is much more predictable and linear. As needed add loop gain by adding gain to U2 via boosting R4. I'm also wondering if a series RC from Q2 collector to U2 - input might also help kill oscillation.

" boosting R4 " you mean increasing the value of R4

MisterBill2

- Joined Jan 23, 2018

- 27,387

Until the capacitors charge to a stable voltage the circuit will not be in the stable conditions. Designing to avoid startup transients is often a challenge. Just exactly WHAT is C1 (22nF) doing for you?? That is undoubtedly the source of your spike, aside from the effects of assorted stray couplings.

That is a PI controller. C1 is a part of that.Until the capacitors charge to a stable voltage the circuit will not be in the stable conditions. Designing to avoid startup transients is often a challenge. Just exactly WHAT is C1 (22nF) doing for you?? That is undoubtedly the source of your spike, aside from the effects of assorted stray couplings.

please see the file

Attachments

-

6.3 KB Views: 3

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin