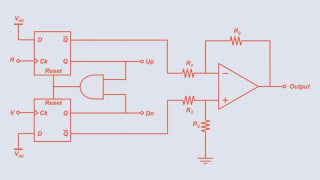

The exact information on SPI communication is not explicitly stated so I'm guess there's a little bit "reading between the lines" should be employed.

According to my ability to read timing diagrams and reading between the lines...

MISO(sdo) is mode 1 and MOSI (sdi) is mode 0

And WR/FSYNC plays the role of Slave Select. Where does the clock phase and polarity come into play

Except from ad2s1210 datasheet

SERIAL INTERFACE

The serial interface is selected by holding the SOE pin low. The AD2S1210 serial interface consists of four signals: SDO, SDI,

WR/FSYNC, and SCLK. The SDI is used for transferring data into the on-chip registers whereas the SDO is used for accessing

data from the on-chip registers, including the position, velocity, and fault registers. SCLK is the serial clock input for the device, and all data transfers (either on SDI or SDO) take place with respect to this SCLK signal. WR/FSYNC is used to frame the data. The falling edge of WR/FSYNC takes the SDI and SDO lines out of a high impedance state. A rising edge on WR/FSYNC returns the SDI and SDO to a high impedance state. The CS input is not required for the serial interface and should be held low. SDO Output In normal mode of operation, data is shifted out of the device as a 24-bit word under the control of the serial clock input, SCLK. The data is shifted out on the rising edge of SCLK. The timing diagram for this operation is shown in Figure 32. SDI Input The SDI input is used to address the on-chip registers and as a daisy-chain input in configuration mode. The data is shifted into the part on the falling edge of SCLK. The timing diagram for this operation is shown in Figure 32

According to my ability to read timing diagrams and reading between the lines...

MISO(sdo) is mode 1 and MOSI (sdi) is mode 0

And WR/FSYNC plays the role of Slave Select. Where does the clock phase and polarity come into play

Except from ad2s1210 datasheet

SERIAL INTERFACE

The serial interface is selected by holding the SOE pin low. The AD2S1210 serial interface consists of four signals: SDO, SDI,

WR/FSYNC, and SCLK. The SDI is used for transferring data into the on-chip registers whereas the SDO is used for accessing

data from the on-chip registers, including the position, velocity, and fault registers. SCLK is the serial clock input for the device, and all data transfers (either on SDI or SDO) take place with respect to this SCLK signal. WR/FSYNC is used to frame the data. The falling edge of WR/FSYNC takes the SDI and SDO lines out of a high impedance state. A rising edge on WR/FSYNC returns the SDI and SDO to a high impedance state. The CS input is not required for the serial interface and should be held low. SDO Output In normal mode of operation, data is shifted out of the device as a 24-bit word under the control of the serial clock input, SCLK. The data is shifted out on the rising edge of SCLK. The timing diagram for this operation is shown in Figure 32. SDI Input The SDI input is used to address the on-chip registers and as a daisy-chain input in configuration mode. The data is shifted into the part on the falling edge of SCLK. The timing diagram for this operation is shown in Figure 32

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin