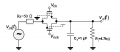

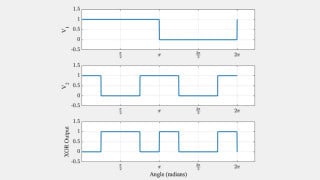

Hey guys, in my last lab work i found a question that none of my classmates could help me with, and im not sure about the answer either. The circuit in question is an ADC with a transmission gate as a analog switch. The question of justifying the transitory of a signal when the clock changes state. V(2) is the tension after the 50ohm resistor. When the clock signal goes down happens the same thing but with the spike being up. Does it have to do with injection charge as we switch the transistor? I changed the rise and fall time of the clock for slower times(from 10p to 100n) and these transitions were gone, which made me think it might have something to do with the capacitor.

Sorry if my english is not the best, im not a native speaker.

Kind Regards,

Francisco

Sorry if my english is not the best, im not a native speaker.

Kind Regards,

Francisco

Attachments

-

61.8 KB Views: 14

-

37.1 KB Views: 12

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin