I'm looking at an SPI signal generated by a test app running in a loop.

Take a look at this:

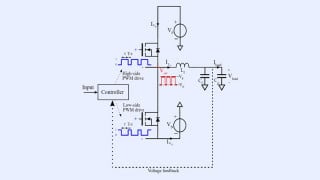

Look at D4, this is the MISO signal coming into the Nucleo F446RE board from an attached nRF24L01.

The value we read - 0E - is correct and is what I expect and is what I see in the debugger if I look, but notice the short low spike, occurring just after the 7th clock pulse.

If I "zoom in" I can see the pulse is about 7 nS:

Far to short it seems to be a legitimate aspect of SPI and far too short to impact the value we receive (0E) but that kind of thing can surely be a risk, it could have unanticipated consequences in certain situations or designs, couldn't it?

Is this common with SPI though? is it harmless because it falls within "tolerances" and so on? If I adjust the code so that that specific byte occurs in a different order, I can see that it seems to be specific to the case where the MCU sends a 0D.

It seems to be that case that it occurs whenever MOSI goes low at the same instant a clock pulse goes low, when these occur at the same time (or close to) we see the glitch on the MISO signal...

This is the SPI init code by the way.

Take a look at this:

Look at D4, this is the MISO signal coming into the Nucleo F446RE board from an attached nRF24L01.

The value we read - 0E - is correct and is what I expect and is what I see in the debugger if I look, but notice the short low spike, occurring just after the 7th clock pulse.

If I "zoom in" I can see the pulse is about 7 nS:

Far to short it seems to be a legitimate aspect of SPI and far too short to impact the value we receive (0E) but that kind of thing can surely be a risk, it could have unanticipated consequences in certain situations or designs, couldn't it?

Is this common with SPI though? is it harmless because it falls within "tolerances" and so on? If I adjust the code so that that specific byte occurs in a different order, I can see that it seems to be specific to the case where the MCU sends a 0D.

It seems to be that case that it occurs whenever MOSI goes low at the same instant a clock pulse goes low, when these occur at the same time (or close to) we see the glitch on the MISO signal...

This is the SPI init code by the way.

Attachments

-

15.1 KB Views: 2

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin