Hello everyone!

I need to plan and build in Logisim Evolution a Moore FSM that displays on a 7-segment display the sequence: '3','1','6','2','5','7','4','1','9','.' (one by one) + the decimal point at the end.

If the system input X=0, then the sequence will be displayed one by one from left to right (including the decimal point).

If the system input X=1, then the sequence will be displayed one by one from right to left (including the decimal point).

I am allowed to use D-FFs + logic gates, and can't use a binary counter or another logic components.

What did I try?

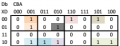

I defined 9 states for the digits, each state represents the binary combination of a digit.

3 = 0011, 1 = 0001, 6 = 0110, and so on.. where Q3=MSB and Q0=LSB.

The 10th state that I defined is 1010 for the decimal point, and I want to turn it on by using an AND gate between Q3 & Q1 once the system arrives to the state 1010.

I built a states diagram + states table:

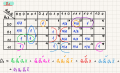

Then I created a 5-vars Karnaugh map for each input of the FFs and found the logic functions.

For example:

Then I built the final circuit in Logisim-Evolution, but the system doesn't work, for now the 7-segment display shows me just "0" without doing anything.

**I used a 7-segment to BCD component to transfer the output combination Q3Q2Q1Q0 for the 7-segment in each clock cycle!

If anyone sees any problem or mistake in my calculations please help me to figure it out!

Thank you in advance for any help!!

I need to plan and build in Logisim Evolution a Moore FSM that displays on a 7-segment display the sequence: '3','1','6','2','5','7','4','1','9','.' (one by one) + the decimal point at the end.

If the system input X=0, then the sequence will be displayed one by one from left to right (including the decimal point).

If the system input X=1, then the sequence will be displayed one by one from right to left (including the decimal point).

I am allowed to use D-FFs + logic gates, and can't use a binary counter or another logic components.

What did I try?

I defined 9 states for the digits, each state represents the binary combination of a digit.

3 = 0011, 1 = 0001, 6 = 0110, and so on.. where Q3=MSB and Q0=LSB.

The 10th state that I defined is 1010 for the decimal point, and I want to turn it on by using an AND gate between Q3 & Q1 once the system arrives to the state 1010.

I built a states diagram + states table:

Then I created a 5-vars Karnaugh map for each input of the FFs and found the logic functions.

For example:

Then I built the final circuit in Logisim-Evolution, but the system doesn't work, for now the 7-segment display shows me just "0" without doing anything.

**I used a 7-segment to BCD component to transfer the output combination Q3Q2Q1Q0 for the 7-segment in each clock cycle!

If anyone sees any problem or mistake in my calculations please help me to figure it out!

Thank you in advance for any help!!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin