I have a few TLE2426CLP TO-92 sometimes called a "rail splitter"

I would like to source 4mA reference and split 5.000Vdc reference, possibly trim dual output reference to ±2.500

The dual polarity supply before used (2) 1% resistors, thermal drift sometimes ±2.547V having 8mV noise

How would you show that the engineered TLE2426 can improve the new supply performance?

The TI TLE2426 datasheet Rail Splitter Precision Virtual Grounds datasheet (Rev. D)

****************************************************************************

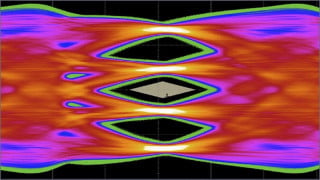

LTspice updated .subckt for TLE2426 for convenience... I anticipate small VGND stability issues; decoupling and VGND/GND bulk cap.

I can show the circuit, breadboard, multimeter results I hope to make the circuit clear as the forum often gets virtual ground questions.

This is better handled with qualified instruction and a standard circuit that is available is LTspice.

I would like to source 4mA reference and split 5.000Vdc reference, possibly trim dual output reference to ±2.500

The dual polarity supply before used (2) 1% resistors, thermal drift sometimes ±2.547V having 8mV noise

How would you show that the engineered TLE2426 can improve the new supply performance?

The TI TLE2426 datasheet Rail Splitter Precision Virtual Grounds datasheet (Rev. D)

****************************************************************************

LTspice updated .subckt for TLE2426 for convenience... I anticipate small VGND stability issues; decoupling and VGND/GND bulk cap.

I can show the circuit, breadboard, multimeter results I hope to make the circuit clear as the forum often gets virtual ground questions.

This is better handled with qualified instruction and a standard circuit that is available is LTspice.

Code:

* TLE2426 enhanced behavioral model

* Pins: VIN VOUT GND

.SUBCKT TLE2426 VIN VOUT GND

*.params (tune as needed)

.PARAM Vmin=3.6 ; minimum VIN for regulation (V)

.PARAM Rout=0.8 ; output impedance (ohms)

.PARAM gm=20 ; loop transconductance (S)

.PARAM Imax=35m ; approx max source/sink (A)

.PARAM Vhead=0.1 ; headroom around target for softer limiting (V)

* Compute regulation target (midpoint)

BVTGT VTGT GND V = { V(VIN,GND)/2 }

* Error between target and actual output

BVER VERR GND V = { V(VTGT,GND) - V(VOUT,GND) }

* Regulation enable based on VIN >= Vmin

* EN is 1 when VIN >= Vmin, else 0 (no regulation; output floats via Rout)

BEN EN GND V = { V(VIN,GND) >= Vmin ? 1 : 0 }

* Ideal drive current before limiting

BIDR IDR GND I = { EN * gm * V(VERR,GND) }

* Soft current limiter: clamp to +/- Imax as error grows

* Linear region within +/-Vhead around target; clamps outside

BILIM ILIM GND I = {

EN ? limit( gm*V(VERR,GND), -Imax, Imax ) : 0

}

* Drive output with limited current

GOUT VOUT GND VALUE = { I(V(ILIM,GND)) }

* Output resistance (provides load sharing and droop)

Rout VOUT GND {Rout}

* Small numerical stabilizers (optional)

Cstab VOUT GND 1u

Rstab VERR GND 1Meg

.ENDS TLE2426

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin