I've seldom used interrupts in the 8051, and then only to manage serial UART communications. Truth is, I don't like interrupts... they mess up program execution timing, which is critical in most of the applications that I've worked on... but I'm sure that the designers put them there for pretty solid set of good reasons...

This time, I need to use timer 0 in mode 1. That is, a 16-bit timer.

Now, I do know how to set up a timer interrupt, and how to configure the timer for that purpose (I think). My question is:

I've already re-read the 8051's hardware manual, but the details still seem a little foggy to my tired brain...

My concern is if the code in the service routine is too large, maybe the timer interrupt will call itself before the routine has been completed and exited, and an endless loop will ensue.... my intuition tells me that the timer will only restart after completing its service routine, but I'd like to hear it from people more experienced than me.

@Papabravo

This time, I need to use timer 0 in mode 1. That is, a 16-bit timer.

Now, I do know how to set up a timer interrupt, and how to configure the timer for that purpose (I think). My question is:

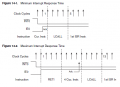

- Does the timer stop when execution is vectored to its corresponding routine and then restarts when the RETI instruction is encountered?

- Or does the timer resets itself immediately upon vectoring and starts running again regardless if its service routine has been completed or not?

I've already re-read the 8051's hardware manual, but the details still seem a little foggy to my tired brain...

My concern is if the code in the service routine is too large, maybe the timer interrupt will call itself before the routine has been completed and exited, and an endless loop will ensue.... my intuition tells me that the timer will only restart after completing its service routine, but I'd like to hear it from people more experienced than me.

@Papabravo

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin