Hello everyone,

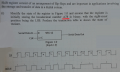

I do this problem on Shift Registers (SISO)....

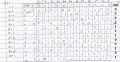

I do truth table for shift register, but I think there are problem in waveform in

{Q0''FF0'' = I choose Data in "1" for start and complete same the line }

in {Q1 "FF1" = I choose data in "0" in clk "1" use "0" because"shift "}

in{Q2 "FF2" = I choose data in "1" in clk "1" "2" use "1" because"shift "} ......... .

I do waveform from Q0 to Q5 because there isn't space

what different between SISO and SIPO in sketch truth table and waveform?

thanks a lot,

sorry for me poor English ....

I do this problem on Shift Registers (SISO)....

I do truth table for shift register, but I think there are problem in waveform in

{Q0''FF0'' = I choose Data in "1" for start and complete same the line }

in {Q1 "FF1" = I choose data in "0" in clk "1" use "0" because"shift "}

in{Q2 "FF2" = I choose data in "1" in clk "1" "2" use "1" because"shift "} ......... .

I do waveform from Q0 to Q5 because there isn't space

what different between SISO and SIPO in sketch truth table and waveform?

thanks a lot,

sorry for me poor English ....

Attachments

-

417.8 KB Views: 57

-

445.2 KB Views: 60

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin