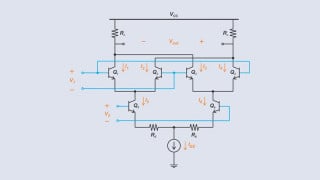

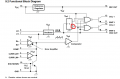

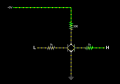

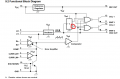

I was working on an smps design using SG3524N but found out something confusing in the datssheet of the SG3524N. The datasheet shows that internally the two transistors will give output complemented to each other as shown.

But there is a design of flyback where both of the collector and emitter are shorted. Now suppose the first transistor is high and other is low, then the current will flow in the circuit using the first transistor, but in the other cycle the same will happen because now the second transistor is ON and the second one is OFF and current again flows due to the second one.

This shows that the current is continously flowing and there is no duty cycle generated. How is this working???Kindly help me in this confusion if I am understanding it wrong.

But there is a design of flyback where both of the collector and emitter are shorted. Now suppose the first transistor is high and other is low, then the current will flow in the circuit using the first transistor, but in the other cycle the same will happen because now the second transistor is ON and the second one is OFF and current again flows due to the second one.

This shows that the current is continously flowing and there is no duty cycle generated. How is this working???Kindly help me in this confusion if I am understanding it wrong.

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin