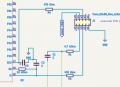

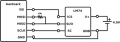

I’m working with some sort of proprietary MCU to MCU serial protocol form 2008. On the master side it’s a boiler and the slate side is a small display and keypad that shows the boiler temp which is what I’m trying to capture for my home automation system. the key pad can change parameters of the boiler so the protocol can send data both ways. There is only clock, data, and ground between the 2 MCUs. I’ve researched every serial protocol I could find and none fit the description (It is absolutely not i2c or SPI).

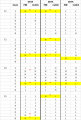

The protocol when the master is sending data seems simple enough…..every 100ms 6 bytes are transmitted separated by 200us between bytes. I think I’ve figured out which of the 6 bytes is the data I’m looking for and I can ignore the rest. But the thing that’s driving Me crazy is some data bits appear to come early and out of sync with the clock.

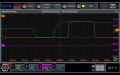

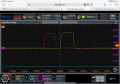

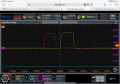

Ive spent hours looking at this and it seems that 3us before the clock goes high the data line goes high or low. Normally when the clock is low the data line is floating (high impedence) from the tranmistting (master) MCU and gets pulled down on the PCB board of the receiving MCU (slave) And shows low. But at 3us prior to clock going high the master MCU pulls the data line low or high For some reason. If the data bit is low then I get a pulse ahead of the clock pulse. If the data bit is high in this scenario the width of my data pulse is 3us wider. If the master pulls data low before a clock pulse it looks normal because the data line is normally Pulled low anyway by the slave.

kinda hard to explain but simply put - what would be the purpose of a data line going high or low during Transmission of bits within a byte frame when the clock is low? With ic2 and SPI i believe usign the data line when clock is low signals start and stop. But in my case this seems to happen before every bit transmitted. Also I can’t determine any kind of pattern When the data line goes low or high ahead of the clock. Sometimes it goes high on the 3 bit of the 4th byte and other times it’s the 1st bit of the 3rd byte, etc.

am I chasing a phantom problem Or can anyone explain why a designer would use the state of the data line ahead of a clock pulse for 2 wire serial protocol? Here is an example of when data line goes high ahead of a zero data bit…

The protocol when the master is sending data seems simple enough…..every 100ms 6 bytes are transmitted separated by 200us between bytes. I think I’ve figured out which of the 6 bytes is the data I’m looking for and I can ignore the rest. But the thing that’s driving Me crazy is some data bits appear to come early and out of sync with the clock.

Ive spent hours looking at this and it seems that 3us before the clock goes high the data line goes high or low. Normally when the clock is low the data line is floating (high impedence) from the tranmistting (master) MCU and gets pulled down on the PCB board of the receiving MCU (slave) And shows low. But at 3us prior to clock going high the master MCU pulls the data line low or high For some reason. If the data bit is low then I get a pulse ahead of the clock pulse. If the data bit is high in this scenario the width of my data pulse is 3us wider. If the master pulls data low before a clock pulse it looks normal because the data line is normally Pulled low anyway by the slave.

kinda hard to explain but simply put - what would be the purpose of a data line going high or low during Transmission of bits within a byte frame when the clock is low? With ic2 and SPI i believe usign the data line when clock is low signals start and stop. But in my case this seems to happen before every bit transmitted. Also I can’t determine any kind of pattern When the data line goes low or high ahead of the clock. Sometimes it goes high on the 3 bit of the 4th byte and other times it’s the 1st bit of the 3rd byte, etc.

am I chasing a phantom problem Or can anyone explain why a designer would use the state of the data line ahead of a clock pulse for 2 wire serial protocol? Here is an example of when data line goes high ahead of a zero data bit…

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin