Hello all, I'm new to the forum and could do with some help.

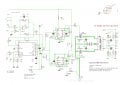

I built 2 off dc-dc push-pull inverters which appear to basically work, however, occasionally blowing FETS. The inverters are designed to essentially behave as isolated constant current sources.

I believe that, as the duty cycle is reduced (when the current limit system comes into play) things go wrong resulting in FETs going short circuit. The problem is that I can't measure what happens when the fault occurs.

When first enabled and at low current ie. at around 90% duty cycle one FET runs slightly warmer than the other. This behaviour is the same on both boards.

After much head scratching and many FET replacements, I decided to go back to basics and run at reduced voltage (48V input 190V output) to try to analyze what's going on and I noticed the voltage on the two FET drains is not quite as expected and not symmetrical, see attached photos.

The system uses a SG3525 driving MCP1406/07 drivers, driving FCH067N65S3 FETs. The transformer consists of 18 turns secondary and 4 + 4 turns primary bifilar wound on a ETD59 e core. I have tried isolating the driver circuit with SI2861BBC drivers as I originally had some noise issues, but then went back to the original 1407 drivers which produce essentially the same but slightly cleaner waveform as you can see from the two photos.

Any pointers would be greatly appreciated - my feeling is that I need to tackle the non symmetrical FET turn off issue first.

Kind regards

I built 2 off dc-dc push-pull inverters which appear to basically work, however, occasionally blowing FETS. The inverters are designed to essentially behave as isolated constant current sources.

I believe that, as the duty cycle is reduced (when the current limit system comes into play) things go wrong resulting in FETs going short circuit. The problem is that I can't measure what happens when the fault occurs.

When first enabled and at low current ie. at around 90% duty cycle one FET runs slightly warmer than the other. This behaviour is the same on both boards.

After much head scratching and many FET replacements, I decided to go back to basics and run at reduced voltage (48V input 190V output) to try to analyze what's going on and I noticed the voltage on the two FET drains is not quite as expected and not symmetrical, see attached photos.

The system uses a SG3525 driving MCP1406/07 drivers, driving FCH067N65S3 FETs. The transformer consists of 18 turns secondary and 4 + 4 turns primary bifilar wound on a ETD59 e core. I have tried isolating the driver circuit with SI2861BBC drivers as I originally had some noise issues, but then went back to the original 1407 drivers which produce essentially the same but slightly cleaner waveform as you can see from the two photos.

Any pointers would be greatly appreciated - my feeling is that I need to tackle the non symmetrical FET turn off issue first.

Kind regards

Attachments

-

317.7 KB Views: 8

-

4.7 MB Views: 14

-

3.7 MB Views: 14

Last edited by a moderator:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin