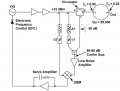

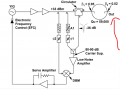

Hello , I am building a system shown below ,it consists of a YIG which is the reference oscilator and the main oscilator.

Yig is a device which changes its voltage as a function of voltage.

the main oscillator oscillates at a constant frequency always.

the mixer compares the reference oscillator frequency with the main oscillator frequency and produce voltage proprtional to the difference between the two.its called error voltage as shown bellow and the attached article.

The YIG device changes its output frequency by the amount of voltage it gets from the servo Amplfier.

if we look into general control theory of PID shown below we see that we need to track the desired signal and eventually get the error voltage to reduce.

I can make a transfer function of them amplifier.

I also can try and do a table of by how much my YIG changes its frequency as a function of voltage.

Also i can record the initial error voltage between the YIG and the main oscillator.

but how can i combine them and see if my SERVO amplifier can do the job and succeed in making a lock of the YIG oscillator and main oscillator?

Thanks.

Yig is a device which changes its voltage as a function of voltage.

the main oscillator oscillates at a constant frequency always.

the mixer compares the reference oscillator frequency with the main oscillator frequency and produce voltage proprtional to the difference between the two.its called error voltage as shown bellow and the attached article.

The YIG device changes its output frequency by the amount of voltage it gets from the servo Amplfier.

if we look into general control theory of PID shown below we see that we need to track the desired signal and eventually get the error voltage to reduce.

I can make a transfer function of them amplifier.

I also can try and do a table of by how much my YIG changes its frequency as a function of voltage.

Also i can record the initial error voltage between the YIG and the main oscillator.

but how can i combine them and see if my SERVO amplifier can do the job and succeed in making a lock of the YIG oscillator and main oscillator?

Thanks.

Attachments

-

563.8 KB Views: 18

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin