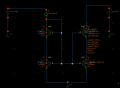

Poor Man's Cascode current mirror

- Thread starter SeanV123

- Start date

Scroll to continue with content

I want to find the conditions of the devices to get all devices in saturationIf You will do an Internet-Search, You can spend all day going over various Current-Mirror designs.

It would help if You would state what it is that You are trying to accomplish,

and why You particularly want a Cascode-Configuration.

.

.

.

Yes, the question is “size the transistors so that each transistor is biased in saturation. What are the golden conditions that put each transistor in saturation and has the circuit behaving like a regular cascode current mirror ?” I tried adjusting the size of N5 and N8 so that the source voltage is larger, hence increasing the drain voltage of the mirror devicesIs this a Homework question ?

.

.

.

With the FETs in "Saturation",

the Circuit will not be performing as a Current-Mirror of any type or configuration.

This sounds like a trick question to see if You are paying attention and

understanding what is supposed to be occurring in this Circuit,

and possibly, what the condition of "Saturation" means.

.

.

.

the Circuit will not be performing as a Current-Mirror of any type or configuration.

This sounds like a trick question to see if You are paying attention and

understanding what is supposed to be occurring in this Circuit,

and possibly, what the condition of "Saturation" means.

.

.

.

With the FETs in "Saturation",

the Circuit will not be performing as a Current-Mirror of any type or configuration.

This sounds like a trick question to see if You are paying attention and

understanding what is supposed to be occurring in this Circuit,

and possibly, what the condition of "Saturation" means.

.

.

.

[/QUOTE

That’s what I was thinking, shouldn’t the upper transistors be in triode region?

yes I know, these are FETsIf you are not aware, the saturation definition for a FET is different than for a BJT.

.yes I know, these are FETs

OK, Fine,

now tell us what the requirements are to have a FET in Saturation.

And then note that all of the FETs have their Gates connected together,

but the various Sources and Drains are at different potentials from Ground.

.

.

.

Vds > vgs-vth. But if all the gates are equal to the drain of N5, where does that leave me?.

OK, Fine,

now tell us what the requirements are to have a FET in Saturation.

And then note that all of the FETs have their Gates connected together,

but the Sources and Drains are at different potentials from Ground.

.

.

.

That's why I said that it looks like a trick-question.

But don't get me wrong,

I ,literally, don't know what I'm talking about in this case.

I had to look-up the definition of Saturation, as I never use the term, or definition,

but I'm just a Genius-Hobbyist who's reasonably good at

interpreting performance-graphs in a Spec-Sheet,

not a proffesional EE.

It looks to me like an impossible conundrum,

which can never result in a stable condition, as outlined in the original question,

but I could be missing something.

.

.

.

But don't get me wrong,

I ,literally, don't know what I'm talking about in this case.

I had to look-up the definition of Saturation, as I never use the term, or definition,

but I'm just a Genius-Hobbyist who's reasonably good at

interpreting performance-graphs in a Spec-Sheet,

not a proffesional EE.

It looks to me like an impossible conundrum,

which can never result in a stable condition, as outlined in the original question,

but I could be missing something.

.

.

.

The cascade arrangement for differential pair is sort of related. Just talking about CC.

A discussion of constant current using n-enhancement mosfet shown in the video is slightly mathematical,

the formula uses square root. When you see the simulation results the accomplished goal of CC circuit is shown.

A discussion of constant current using n-enhancement mosfet shown in the video is slightly mathematical,

the formula uses square root. When you see the simulation results the accomplished goal of CC circuit is shown.

Last edited:

I wish this discussion had gotten more into the supposed

"length" and "width" discrepancies typically found in MOSFETs,

and any trends regarding the other usual FET specifications that

might be expected to be found to "usually" have "more", or "less", "length", and "width", discrepancies.

And, are the usual discrepancies normally found to be in the ~0.01% range, or the ~10%+ range.

Instead, these known discrepancies are completely ignored and "Zeroed-Out" in the presented calculations.

.

.

.

"length" and "width" discrepancies typically found in MOSFETs,

and any trends regarding the other usual FET specifications that

might be expected to be found to "usually" have "more", or "less", "length", and "width", discrepancies.

And, are the usual discrepancies normally found to be in the ~0.01% range, or the ~10%+ range.

Instead, these known discrepancies are completely ignored and "Zeroed-Out" in the presented calculations.

.

.

.

| Thread starter | Similar threads | Forum | Replies | Date |

|---|---|---|---|---|

|

|

Poor man's cascode current mirror | Analog & Mixed-Signal Design | 1 | |

| K | Poor Man's Voltage Reference | Analog & Mixed-Signal Design | 8 | |

| R | Poor Man's Transmitter for Pet Containment System | General Electronics Chat | 53 | |

|

|

Project: Poor Man's Calorimeter | General Electronics Chat | 9 | |

| J | poor man's oscilloscope | Microcontrollers | 1 |

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin