Hello. My first time here and I'm sure I'll make at least a few mistakes. I've searched but can't find an answer to my question so I'm hoping I can find it this way. My EE knowledge is pretty rusty as you'll soon see - thanks for your patience as you read on ...

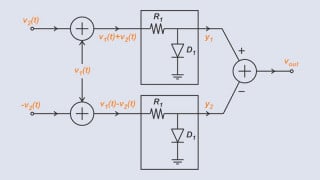

The diagram attached shows a single coil to be pulsed by n & p FETs. Each FET has 100V d-s breakdown and < 10 mOhm Rds. Vgs is +/-2V for each. There is no possibility of both FETs ever switching on at the same time.

The coil is ~ 50mH & Vdd may be as low as 12V and as high as 50V as I experiment with pulse widths, duty cycles and field strengths. I realize back EMF may be significant, but I'm not sure how to protect the FETs. Current demand per pulse will be way below FET capability.

I realize this circuit will need a lot of work and caps added to lessen ringing/noise, but my concern for now is to protect the FETs. I also realize I'm a bit challenged with regard to correct wiring of T2. I ran out of time - sorry about the mess. The ESP32 is a 3.3V device.

Last point which I'm sure some will ask me regards pulse widths and duty cycle. The hope is to create pulses at widths between 0.1ms and 2ms. Duty cycle flexible depending on noise, heat, ringing and of effects from back EMF. The ideal case which I don't expect to achieve: 0.5ms pulses that aren't a terrible mess (some ringing/noise will be acceptable). Current approx 0.5A. Duty cycle 0.3 max. Just the ideal case. The final result can be far off from this and I'll be happy.

Many thanks for your help. I'll be surprised if my diagram doesn't have horrible flaws. I'm just getting back into this so please go easy on me!

The diagram attached shows a single coil to be pulsed by n & p FETs. Each FET has 100V d-s breakdown and < 10 mOhm Rds. Vgs is +/-2V for each. There is no possibility of both FETs ever switching on at the same time.

The coil is ~ 50mH & Vdd may be as low as 12V and as high as 50V as I experiment with pulse widths, duty cycles and field strengths. I realize back EMF may be significant, but I'm not sure how to protect the FETs. Current demand per pulse will be way below FET capability.

I realize this circuit will need a lot of work and caps added to lessen ringing/noise, but my concern for now is to protect the FETs. I also realize I'm a bit challenged with regard to correct wiring of T2. I ran out of time - sorry about the mess. The ESP32 is a 3.3V device.

Last point which I'm sure some will ask me regards pulse widths and duty cycle. The hope is to create pulses at widths between 0.1ms and 2ms. Duty cycle flexible depending on noise, heat, ringing and of effects from back EMF. The ideal case which I don't expect to achieve: 0.5ms pulses that aren't a terrible mess (some ringing/noise will be acceptable). Current approx 0.5A. Duty cycle 0.3 max. Just the ideal case. The final result can be far off from this and I'll be happy.

Many thanks for your help. I'll be surprised if my diagram doesn't have horrible flaws. I'm just getting back into this so please go easy on me!

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin