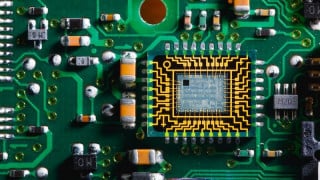

Looking around I saw a PSOC user who did a 24 bit DDS component for

PSOC. A component is on onchip resource inside chip, there are standard

components already done by PSOC IDE, and users can create their own thru

schematic capture and/or Verilog.

This shows two DDS channels implemented on chip, along with clocked wavedac

components clocked by DDS, also onchip. Based on resources looks like chip

could do 4 independent channels

Of course you can sync the channels, set the phase relationship of each channel,

and of course clock rate. Sweep them, etc........

PSOC VDACs used in wavedac, settling time only good enough to clock to 1 Mhz.

One could use the IDACs which are good for 10 Mhz to get higher sine/saw/arbitrary

out of wavedac. Used 64 samples for sine wave, so that limits sine out to roughly 15

Khz. Harmonic distortion high at 100 Khz. Down in the audio region harmonics ~ 35

or better db down. If I used more samples in wavedac configurator that would result in

lower harmonic distortion. I did for trial clock the wavedac VDAC at 6.4 Mhz, still got

a reasonable sine out, but harmonic distortion high.

Looking at right hand resource window not much internal was used to do all this. Lots

of room for other stuff. 4 lines of code use, just start instructions for each component.

Of course to do sweep more code necessary, maybe another 4 -6 lines.

Mixed signal processors with logic fabric entertain some interesting capabilities.

Interesting to contemplate a 4 channel f() generator all on one chip. Although external

components needed to drive 50 ohms.

The DDS direct outputs will clock well into the Mhz range. The above setup

was to yield 1 Hz resolution. Of course if you lower the DDS input clock you

could get centuries for a waveform period.

Regards, Dana.

PSOC. A component is on onchip resource inside chip, there are standard

components already done by PSOC IDE, and users can create their own thru

schematic capture and/or Verilog.

This shows two DDS channels implemented on chip, along with clocked wavedac

components clocked by DDS, also onchip. Based on resources looks like chip

could do 4 independent channels

Of course you can sync the channels, set the phase relationship of each channel,

and of course clock rate. Sweep them, etc........

PSOC VDACs used in wavedac, settling time only good enough to clock to 1 Mhz.

One could use the IDACs which are good for 10 Mhz to get higher sine/saw/arbitrary

out of wavedac. Used 64 samples for sine wave, so that limits sine out to roughly 15

Khz. Harmonic distortion high at 100 Khz. Down in the audio region harmonics ~ 35

or better db down. If I used more samples in wavedac configurator that would result in

lower harmonic distortion. I did for trial clock the wavedac VDAC at 6.4 Mhz, still got

a reasonable sine out, but harmonic distortion high.

Looking at right hand resource window not much internal was used to do all this. Lots

of room for other stuff. 4 lines of code use, just start instructions for each component.

Of course to do sweep more code necessary, maybe another 4 -6 lines.

Mixed signal processors with logic fabric entertain some interesting capabilities.

Interesting to contemplate a 4 channel f() generator all on one chip. Although external

components needed to drive 50 ohms.

The DDS direct outputs will clock well into the Mhz range. The above setup

was to yield 1 Hz resolution. Of course if you lower the DDS input clock you

could get centuries for a waveform period.

Regards, Dana.

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin