MOSFET Latching Circuit

- Thread starter Trent-Janak

- Start date

Scroll to continue with content

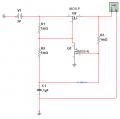

Supply voltage is 3 volts and the battery i realize is drawn backwards. As far as the polarity and type of FETs is where i am unsure.

There are many types of FETs. You should be more specific. Part numbers would clear things up, but you're the one asking for help and you shouldn't make that any more difficult for us than it has to be.As far as the polarity and type of FETs is where i am unsure.

Ok let me go a layer deeper. The specific circuit is for our senior design project, and our professor drew up the circuit as an example of what we could use. I do not know what type of FETs to use, since i do not have any prior experience with them.

Will you be graded for this project?The specific circuit is for our senior design project

No i wont be graded. I will graduate if i have a working prototype, and continue working on it until i get a working prototype if i do notWill you be graded for this project?

There is no need for it to be turned off. Basically a single throw switch. And i used on P and one N FetCan you use more than 3V?

3V will require a MOSFET with a very low threshold voltage, Vgs(th), of less than 2V maximum.

What polarity MOSFETs did you use (N or P channel)?

How will the latch be turned off once it is latched?

Which is which?i used on P and one N Fet

How did you simulate this, and with what devices?

i simulated it through multisim, but im not sure which is The P and which is the N. This was drawn for me as an example by our advisory prof. I just cant seem to get it to work and he did not explain all of the detailsWhich is which?

How did you simulate this, and with what devices?

Bordodynov

- Joined May 20, 2015

- 3,430

1mOhm=0.001Ohm, 1MegOhm=1000000 !

Bordodynov

- Joined May 20, 2015

- 3,430

I know this is an old question, but I can't resist to reply.

Trent-Janak, yes, you connected the N and P channel MOSFETs correctly, but your simulation circuit was different from what your prof drew. More specifically, the resistor connecting the gate of the NMOS and GND is missing; that resistor is important to avoid the NMOS gate voltage from floating.

For the input voltage, since the output is connected to GPIO, I am pretty sure the input voltage source should be either 3.3V or 5V. But 3V is fine, just that you need to choose MOSFETs with Vth (gate threshold voltage) much smaller than 3V (and > -3V for PMOS). You can try BSS138 NMOS and BSS84 PMOS since they have Vth around 1.3V and -1.7V, respectively (AO3400 NMOS and AO3401 PMOS also have low Vth and very easy to get and low cost). Take note that most power MOSFETs have high Vth, so avoid using them in your case.

For the record, the circuit drawn by your prof should latch provided that you use MOSFETs with low enough Vth. The only mistake in the diagram is the battery polarity. Once latched, to unlatch it, you temporarily remove the input voltage source. Alternatively, you can temporarily short the output to GND. But take note that the latter technique can cause large instantaneous current through the PMOS unless you attach a current limiting resistor (say 100Ω) between the Drain (D) of the PMOS and Vout.

Trent-Janak, yes, you connected the N and P channel MOSFETs correctly, but your simulation circuit was different from what your prof drew. More specifically, the resistor connecting the gate of the NMOS and GND is missing; that resistor is important to avoid the NMOS gate voltage from floating.

For the input voltage, since the output is connected to GPIO, I am pretty sure the input voltage source should be either 3.3V or 5V. But 3V is fine, just that you need to choose MOSFETs with Vth (gate threshold voltage) much smaller than 3V (and > -3V for PMOS). You can try BSS138 NMOS and BSS84 PMOS since they have Vth around 1.3V and -1.7V, respectively (AO3400 NMOS and AO3401 PMOS also have low Vth and very easy to get and low cost). Take note that most power MOSFETs have high Vth, so avoid using them in your case.

For the record, the circuit drawn by your prof should latch provided that you use MOSFETs with low enough Vth. The only mistake in the diagram is the battery polarity. Once latched, to unlatch it, you temporarily remove the input voltage source. Alternatively, you can temporarily short the output to GND. But take note that the latter technique can cause large instantaneous current through the PMOS unless you attach a current limiting resistor (say 100Ω) between the Drain (D) of the PMOS and Vout.

Last edited:

Facebook

Facebook Google

Google GitHub

GitHub Linkedin

Linkedin